Software Library

Bootloader for dsPIC33A Digital Signal Controllers

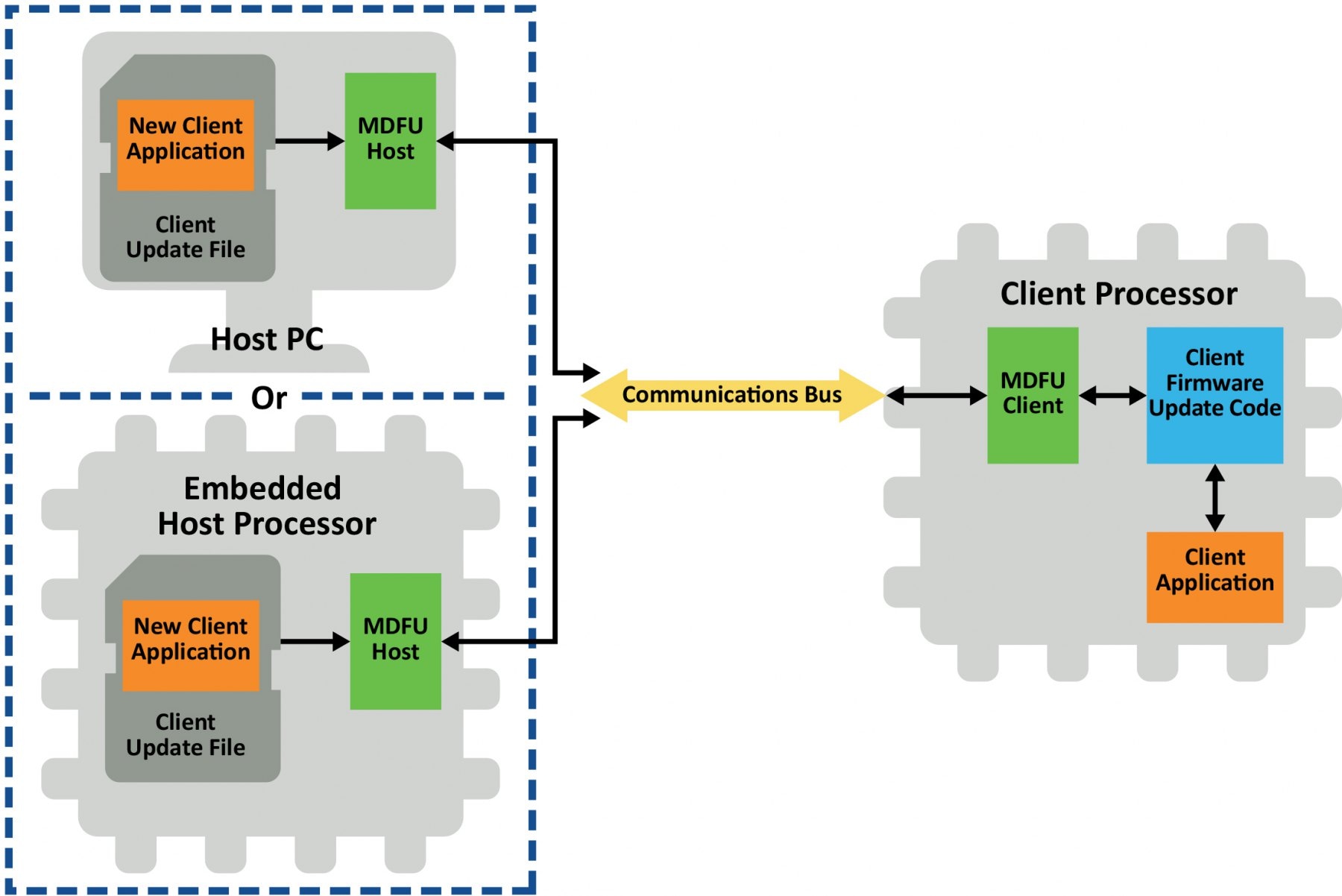

Many embedded system designs need a method for updating a processor's firmware via standard communication buses. The bootloader for dsPIC33A DSCs implements the Microchip Device Firmware Update (MDFU) Protocol, which provides a structured approach for updating the firmware of a client processor using a host processor over various communication interfaces. The figure below illustrates how an MDFU host, which can be either a PC or an embedded processor, transfers a new client application to an MDFU client running on a client processor. The client firmware update code then updates the client application with the new version received from the host.

If you're looking for bootloader support for other dsPIC33 families such as dsPIC33E and dsPIC33C, please visit: Bootloader for dsPIC33 DSCs and PIC24 MCUs

Key Highlights

- Boot loading over UART or CAN-FD using MDFU protocol

- Secure boot and secure firmware upgrades. The bootloader can optionally verify that the application image is correct and authentic using:

- Elliptic Curve Digital Signature Algorithm (ECDSA) with ECC P‑256/SHA‑256 or ECC P‑384/SHA‑384, supported by the Cryptographic Accelerator Module or a software‑based cryptography library.

- Post‑Quantum Cryptographic (PQC) signature algorithm, specifically ML‑DSA‑87 with SHA‑512, supported through the dsPIC33 PQC Library and the Cryptographic Accelerator Module.

- Hybrid PQC and ECDSA secure boot authentication, combining ECDSA with ECC P‑384, ML‑DSA‑87 and SHA‑512

- Secure boot and secure firmware upgrades. The bootloader can optionally verify that the application image is correct and authentic using:

- Immutability

- Adds support for the Security Module on dsPIC33A DSCs in the bootloader, which enables Immutable Root of Trust (IRT), The IRT is a boot segment that is as a read-only section of memory which cannot be modified or accessed by the application image

- Optionally supports the ability to authenticate the application image that it is correct using Cryptographic Accelerator Module before it is allowed to execute

- Multiple application image support

- Bootloader can be configured to maintain the existing active image (not overwrite it) while receiving an updated firmware image

- Enables newly downloaded and updated firmware to be verified for integrity and optionally for authenticity before making it an active firmware image

- Optionally facilitates the maintenance of a Golden Image or Factory Default Image

- Helps to build resiliency in the system

- Anti-rollback protection

- Adds support for a semantic versioning (semver) based version number

Elliptic Curve Digital Signature Algorithm (ECDSA) with ECC P‑256/SHA‑256 or ECC P‑384/SHA‑384, supported by the Cryptographic Accelerator Module or a software‑based cryptography library.

The MDFU protocol offers several important characteristics for supporting the dsPIC33A Digital Signal Controller (DSC) devices. These characteristics include:

- Small Memory Footprint: Efficiently updates firmware while maintaining a small memory footprint

- File Transfer Approach: Uses a simple, stable, and processor-independent file transfer method

- Processor Agnostic: Commands and responses are compatible with various processor architectures

- Host and Client Compatibility: Hosts can update any attached MDFU client processor

- Customization: Supports processor-specific features without modifying the protocol

- Simplicity and Stability: Ensures reliable firmware updates with minimal compatibility issues

- Multiple Communication Interfaces: Easily adds support for new communication buses

- Corruption Detection and Recovery: Includes mechanisms for detecting and recovering from command/response corruption

- Code Reuse: Maximizes code reuse across different communication interfaces

These characteristics make the MDFU protocol a robust and versatile solution for updating the firmware of dsPIC33A DSCs, ensuring compatibility, reliability, and ease of implementation across various embedded system design

To access the complete dsPIC33A DSC MDFU based Bootloader library and demo, visit: dsPIC33A Bootloader and Firmware Upgrade Demo

Online Assets

Products

| Title | Product |

Title |

|---|---|---|

|

dsPIC33AK128MC102

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK128MC102 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK128MC103

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK128MC103 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK128MC105

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK128MC105 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK128MC106

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK128MC106 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK128MPS103

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK128MPS103 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK128MPS105

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK128MPS105 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK128MPS106

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK128MPS106 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK128MPS303

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK128MPS303 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK128MPS305

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK128MPS305 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK128MPS306

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK128MPS306 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MC205

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MC205 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MC206

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MC206 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MC208

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MC208 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MC210

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MC210 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MC505

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MC505 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MC506

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MC506 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MC508

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MC508 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MC510

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MC510 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MPS103

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MPS103 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MPS105

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MPS105 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MPS106

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MPS106 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MPS205

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MPS205 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MPS206

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MPS206 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MPS208

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MPS208 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MPS210

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MPS210 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MPS303

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MPS303 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MPS305

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MPS305 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MPS306

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MPS306 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MPS505

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MPS505 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MPS506

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MPS506 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MPS508

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MPS508 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MPS510

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MPS510 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK256MPS512

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK256MPS512 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK32MC102

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK32MC102 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK32MC103

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK32MC103 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK32MC105

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK32MC105 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK32MC106

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK32MC106 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK512MC505

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK512MC505 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK512MC506

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK512MC506 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK512MC508

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK512MC508 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK512MC510

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK512MC510 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK512MPS212

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK512MPS212 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK512MPS505

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK512MPS505 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK512MPS506

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK512MPS506 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK512MPS508

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK512MPS508 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK512MPS510

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK512MPS510 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK512MPS512

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK512MPS512 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK64MC102

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK64MC102 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK64MC103

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK64MC103 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK64MC105

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK64MC105 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |

|

dsPIC33AK64MC106

200 MHz 32-bit Single-Core Digital Signal Controller (DSC)

|

dsPIC33AK64MC106 | 200 MHz 32-bit Single-Core Digital Signal Controller (DSC) |