Log in to myMicrochip to access tools and benefits. Sign up in just one minute.

Maximize Your Experience: Reap the Personalized Advantages by Completing Your Profile to Its Fullest. Update Here

Stay in the loop with the latest from Microchip. Update your profile while you are at it. Update Here

Complete your profile to access more resources. Update Here

true

Getting Started With SuperFlash® Technology

How to Find the Best NOR Flash Solution for Your Design

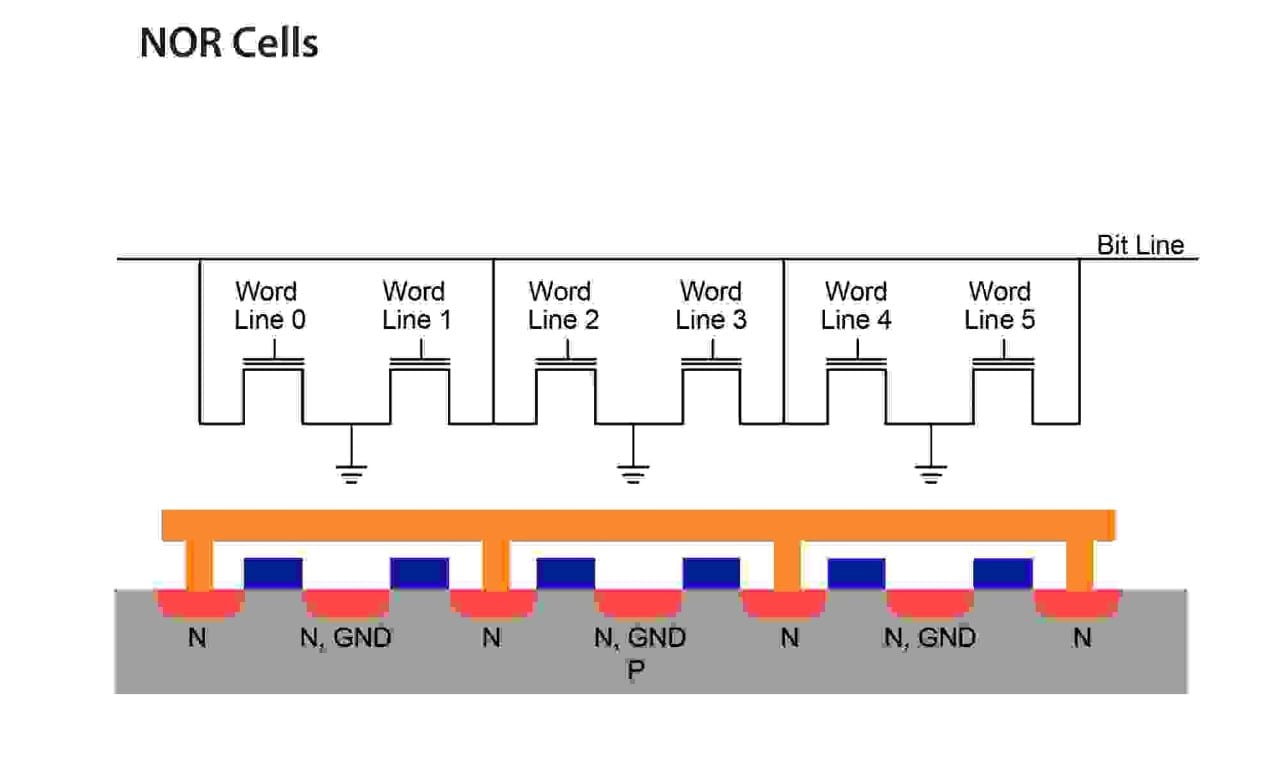

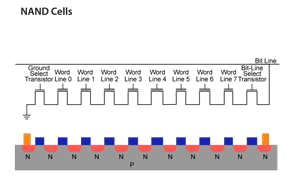

NOR vs. NAND Flash

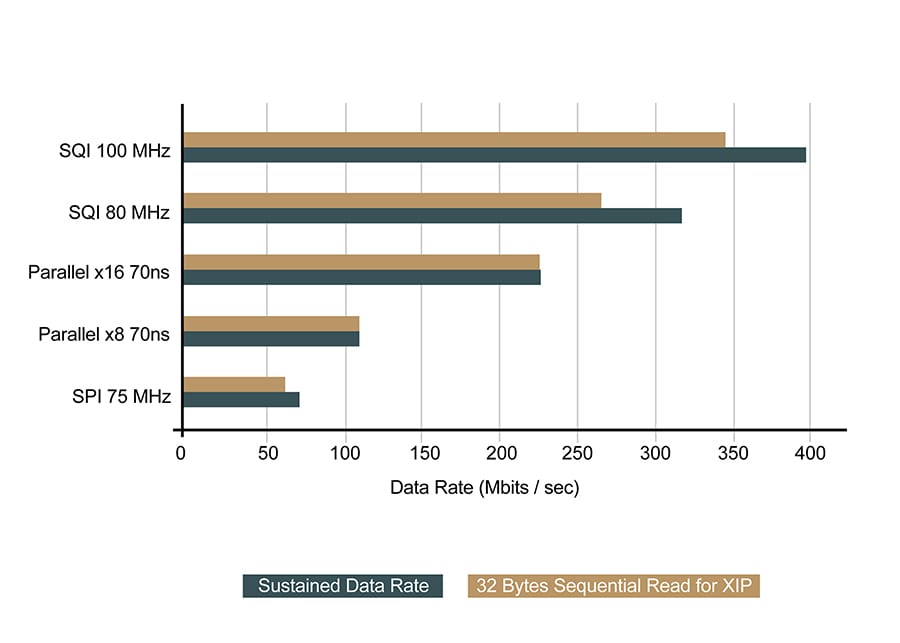

Parallel vs. Serial SPI vs. Serial SQI™ Flash Devices

What Are SQI Flash Devices?

Serial Quad I/O™ (SQI) Flash devices read and write through a 4-bit multiplexed synchronous serial communication interface, which enables true low pin-count, high-bandwidth code Execution-in-Place (XIP) applications. The firmware commands are very similar to those of SPI, but with 4-bit I/O instead of single-bit I/O. Therefore, this interface provides approximately four times the data throughput of SPI. Compared to parallel Flash devices, SQI Flash devices provide very fast performance without requiring large, expensive and high-pin-count packages.