Shaping the Future of Communication with I3C® on the PIC18-Q20

Learn about key partnerships and collaborations with the launch of the first low-pin-count microcontroller with I3C® capability and on-chip level shifting (MVIO).

Introducing PIC18-Q20: Pioneering Low Pin Count MCU

Microchip recently released the exciting PIC18-Q20, the industry’s first low pin count microcontroller (MCU) with up to two I3C® peripherals with internal level shifters to support interfacing with devices operating on multiple voltage domains. The I3C module on this new microcontroller is designed to operate in Target Mode only and will help designers and software developers ease the transition from I2C/SMBus to I3C while allowing lower system costs, reduced design complexity and reduced board space. During the development of PIC18-Q20, Microchip participated with great success at early interoperability I3C events with other industry leaders. This post will discuss those events, some PIC18-Q20 early adopters and partners and provide a brief background on I3C.

I3C

I3C is an exciting new communication protocol developed by the MIPI Alliance and aims to address the need for higher speed, better data transfer and better low power performance required by modern applications in the electronics industry. It is an enhanced version of the widely popular two-wire I2C protocol, and intentionally retains portions of the older protocol to remain backward compatible. However, the re-design of the two-wire bus now allows for both faster data transfer and lower power consumption. While the I3C protocol uses open-drain communication for a few select transactions, it is now possible to switch to push-pull communication during data transfer. This ability to send data in burst mode allows the bus and connected devices to spend more time free and in a low power state. This is critical as adding more devices to an I2C bus can quickly make it unusable, since it relies upon open-drain communication exclusively.

I3C offers a 10x or greater performance improvement over I2C communication using a 12.5 MHz base clock in Standard Date Rate. It also offers new features like the ability for controllers to either broadcast or directly send Common Command Codes (CCC) to devices on the bus. There are many of these highly useful commands. For example, CCC commands give controllers the ability to dynamically assign addresses. They also give controllers the ability to reset devices or reset their I3C module. I3C targets also benefit since they can power on and “Hot-Join” the bus. Additionally, Targets can now send In-Band Interrupts using the SDA and SCL lines, thus reducing board space and the cost of having dedicated interrupt lines between a Target and the Controller.

Figure 1: MIPI I3C Plugfest San Jose, CA (June 2023)

Figure 2: Interoperability Testing with PIC18-Q20

In June of 2023, the MIPI Alliance hosted a Plugfest, bringing together 10 different companies for I3C interoperability testing. With eight Controller devices, 11 Target devices and three protocol analyzers, workshop participants were able to use the collaborative venue to test key features with a broad range of devices. Microchip engineers Max Prasad and Ashish Makthal brought the Q20 to the event and demonstrated the abilities of the Q20 as an I3C Target device.

For a more in-depth look at I3C, check out this video and this blog post from the MIPI Alliance.

The Q20 Can Support Separate Low Voltage Domains

Figure 3: Bus Topology Showing Multiple Voltage Domains Using On-Chip Level Shifters (MVIO)

A great feature on the PIC18-Q20 is the ability to operate each of the two I3C peripherals on separate voltage domains even down to 1.8 V, while the MCU still operates in a more traditional range of 1.8V–5.5 V. As can be seen in the diagram above, each of the I3C communication lines with MVIO are operated at lower voltages, while the MCU and the I2C bus operate at 5V. By providing on-chip level shifting, the PIC18-Q20 can greatly reduce space and cost in designs.

The vast majority of I3C peripherals released on products in the market have been in Cortex-M23 and M33 devices; the Q20 is the first to offer I3C on 8-bit. As a low-power, small form factor MCU, the Q20 gives developers the ability to bring I3C into a wide range of space sensitive applications including IoT, industrial control, automotive and data centers.

Microchip Partners With Binho

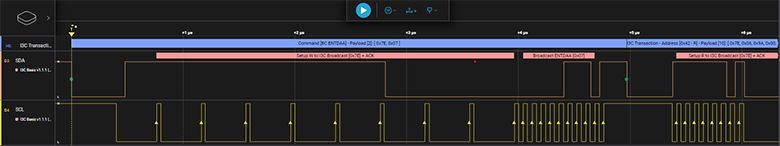

Binho was started in 2015 to help make developing and debugging hardware easier and more enjoyable for everyone. They recently released an I3C BasicSM Protocol Analyzer Plugin for Saleae Logic, a powerful and easy to use tool for debugging I3C transactions. Customers will be excited to learn that Microchip and Binho have partnered together and when customers purchase a PIC-Q20 evaluation kit, they can register to use the plugin free for 45 days. Binho has also released the Binho Supernova, an I3C controller that can be used with the Q20 and supports an I3C operating voltage range of 0.8 V to 3.3 V.

Figure 4: Binho I3C BasicSM Protocol Analyzer Screenshot - Dynamic Address Assignment of the PIC18-Q20

Figure 5: Binho Plugin Analyzer Free Trial QR Code with PIC18-Q20 CNANO

Figure 6: Binho Supernova I3C Controller

Solidigm

Solidigm is a leading innovator in the field of data storage solutions, particularly in the design of Solid State Drives (SSDs) for data centers. They are at the forefront of technological advancements, consistently pushing the boundaries of what's possible in data storage efficiency and performance.

Solidigm has partnered with Microchip Technology and begun using the new PIC18-Q20 microcontroller in their SSD data center designs. During a recent demonstration at the Open Compute Summit’s Global Summit in San Jose, Solidigm showcased an SSD equipped with the Microchip PIC18-Q20 on an Intel EDSFF platform using OpenBMC firmware. The demo highlighted the impressive I3C capability of the system, a feature that the industry is predicted to widely adopt by 2025.

This partnership between Solidigm and Microchip Technology exemplifies the power of collaboration in advancing technology and shaping the future of data storage solutions.

More information about I3C and the PIC18-Q20 family of microcontrollers can be found on our web page and our Getting Started with I3C Using PIC18F16Q20 Microcontroller GitHub Repository.