PIC64: Enabling a New Era of Mission Critical Computing

Microchip has introduced the PIC64HX and PIC64-HPSC families—next-generation 64-bit compute platforms built for environments where failure is not an option. These products are redefining what it means to be mission critical.

In today’s interconnected and increasingly autonomous world, the definition of “mission critical” has evolved. No longer confined to the cockpit of a fighter jet or the flight controller of a launch vehicle, mission-critical computing now extends to autonomous satellites, resilient industrial control systems and secure communications at the tactical edge. The convergence of real-time responsiveness, deterministic networking and resilient security is not a wish list—it’s a necessity.

Yet, traditional embedded architectures are struggling to keep up. Legacy single-core systems can’t meet the growing need for high-throughput parallel processing. Safety-critical workloads are being forced to share space with AI-driven inference engines, network protocol stacks and complex middleware. Meanwhile, evolving standards in Ethernet-based deterministic networking and post-quantum cryptography are reshaping the landscape.

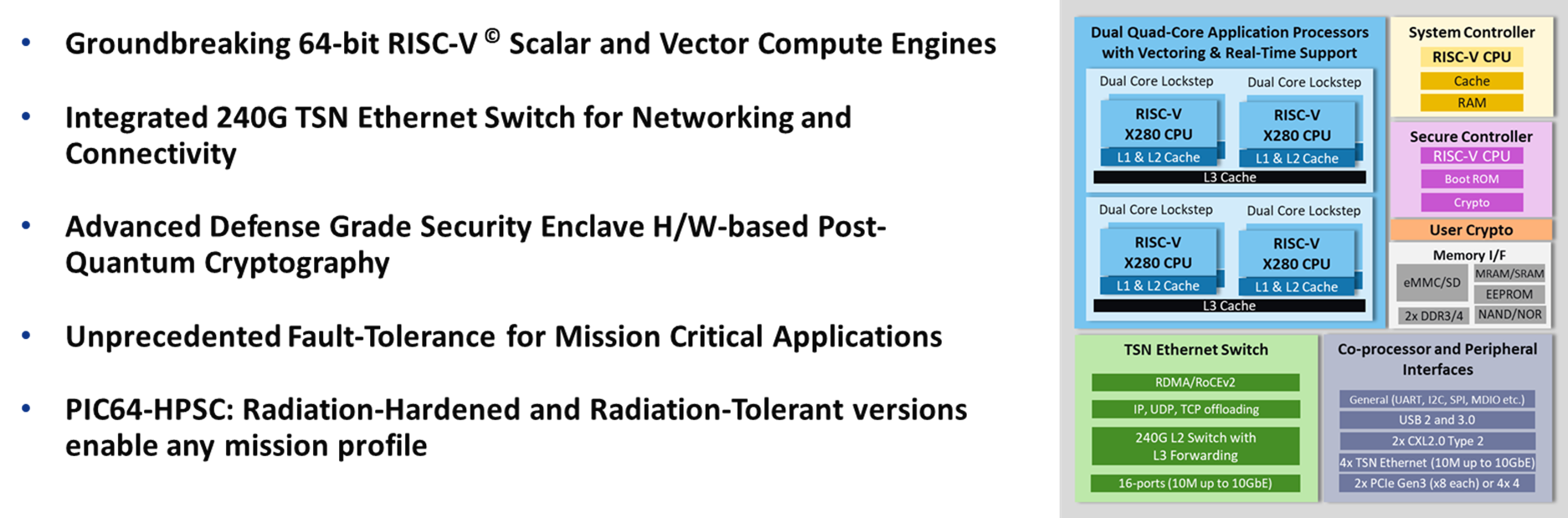

To address this new era of complexity and capability, Microchip has introduced the PIC64HX and PIC64-HPSC families—next-generation 64-bit compute platforms built for environments where failure is not an option. These products are redefining what it means to be mission critical.

Converging Requirements in Aerospace, Defense, Space and Industrial Markets

The requirements across these domains are remarkably similar in spirit, though diverse in implementation:

- Aerospace and Defense demand secure, deterministic and isolated compute environments that can handle real-time mission execution, electronic warfare and advanced ISR (Intelligence, Surveillance, Reconnaissance) applications—all while withstanding extreme environmental conditions and adhering to rigorous certification regimes.

- Space systems, especially those destined for deep space or autonomous operations in LEO/MEO/GEO, must execute flawlessly without ground intervention. That includes fault tolerance, time-sensitive networking and radiation resilience, combined with growing demands for onboard AI processing.

- Industrial automation is rapidly moving toward Industry 4.0. Smart factories, power substations and autonomous robotics now require time-aware networking (like TSN), mixed-criticality software environments and edge AI—all with long lifecycles and deterministic behavior.

Meeting these intersecting demands calls for a compute platform that is scalable, partitioned, secure, network-aware and intelligent. The PIC64HX and PIC64-HPSC rise to this challenge.

Architectural Foundation: 8 RISC-V Cores with Flexible Compute Modes

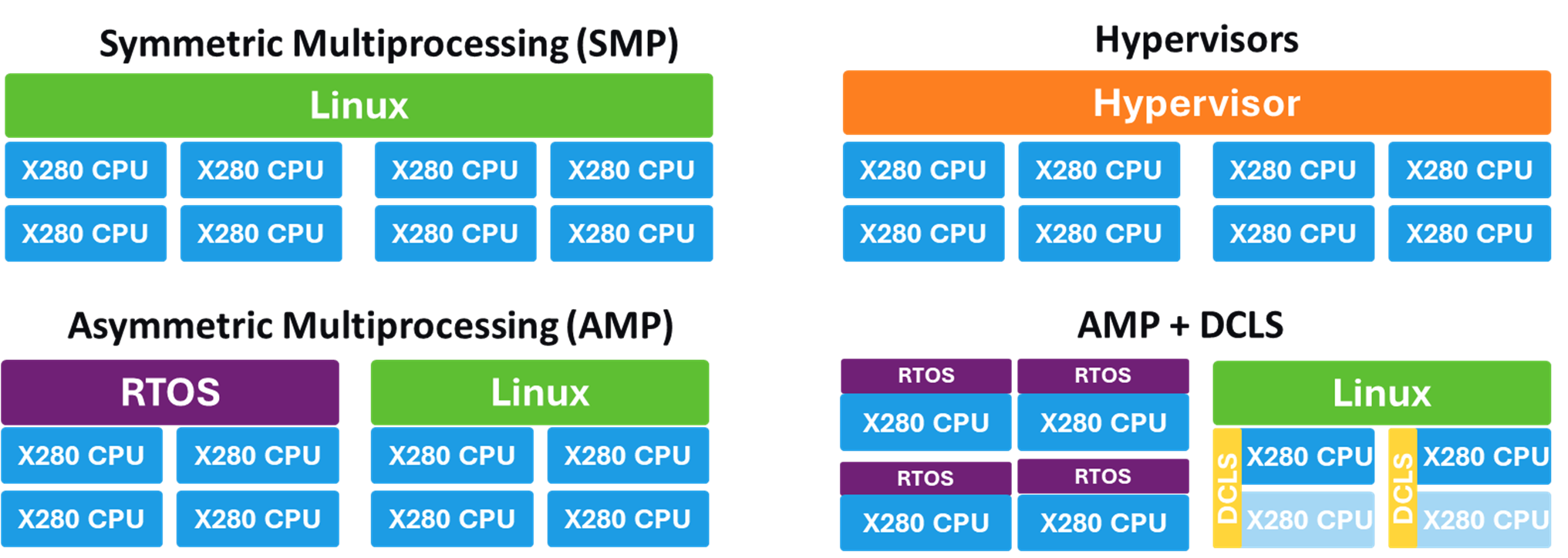

At the heart of both the PIC64HX and PIC64-HPSC lies an innovative 8-core RISC-V architecture, partitioned into two quad-core clusters. This design enables maximum configurability for system integrators:

- SMP (Symmetric Multiprocessing) and AMP (Asymmetric Multiprocessing) modes allow users to tailor compute behavior for performance, isolation or real-time determinism.

- Support for hypervisors makes it possible to host multiple guest OSes or mixed-OS environments, enabling virtualization-based security and workload consolidation.

- For safety-critical functions, the platform offers dual-core lockstep mode—crucial for avionics and spaceflight applications that require SIL-level fault tolerance.

Together, these modes enable time and space partitioning—a must-have for mixed-criticality systems where real-time control logic must coexist with AI inference, user interface software and network stacks.

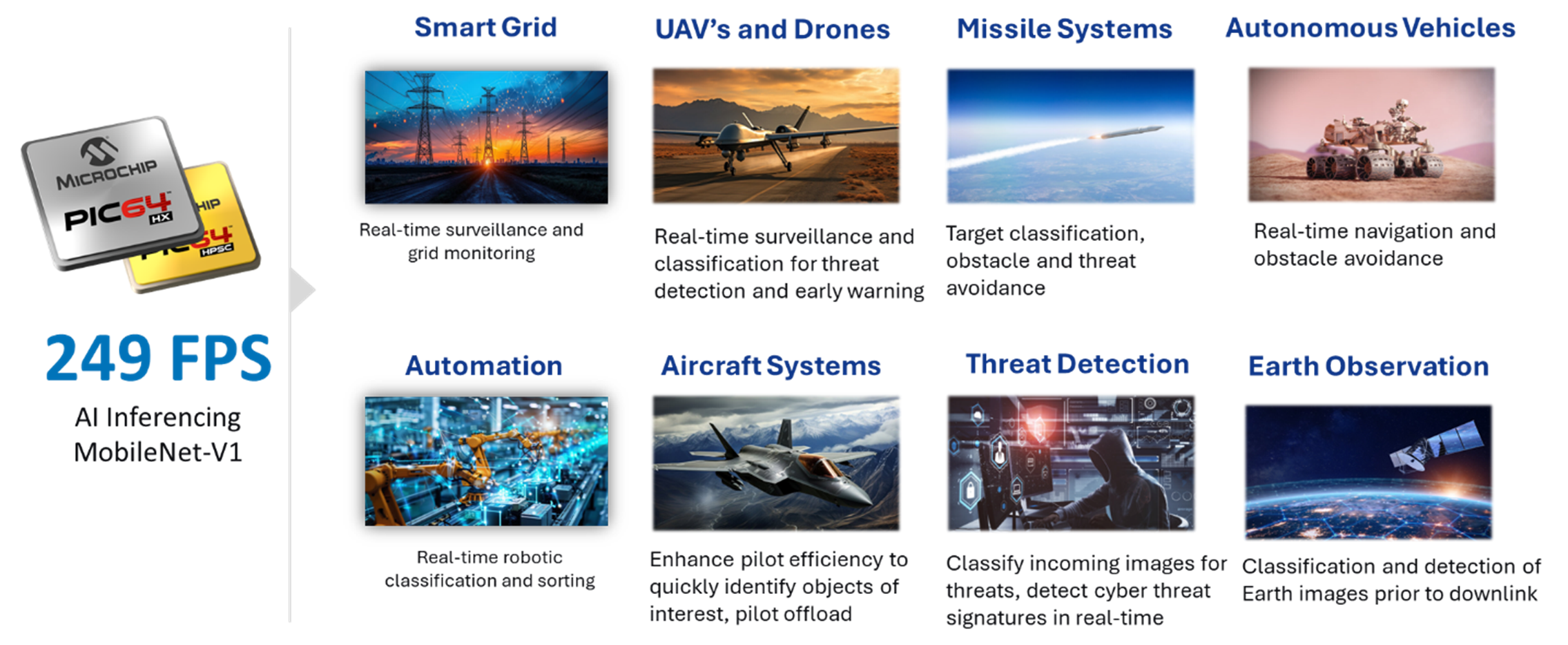

AI/ML Enablement With RISC-V Vector Extensions

Modern mission-critical systems can’t just react—they need to perceive, analyze and adapt in real time. That means integrating AI/ML capabilities natively at the edge.

Both processors support the RISC-V Vector Extension, enabling highly parallelized operations for:

- Image and signal classification

- Sensor fusion

- Predictive maintenance

- Onboard machine vision for autonomous systems

By bringing vectorized AI inferencing closer to the sensor, systems can dramatically reduce latency, power consumption and dependence on ground or cloud infrastructure. The powerful AI and vector engines can support up to 250 frames per second inferencing using MobileNet-V1.

Embedded TSN for Deterministic Networking

Network determinism is no longer optional in time-sensitive domains. The PIC64HX and PIC64-HPSC devices embed a Time-Sensitive Networking (TSN) switch designed to support:

- IEEE P802.1DP for aerospace profiles

- IEC/IEEE 60802 for industrial automation

This onboard TSN features enables synchronized communication across distributed endpoints, including:

- Avionics systems with tight control loop deadlines

- Industrial robots with sub-millisecond cycle times

- Space-based payloads that must coordinate over Ethernet

By integrating TSN into the silicon, these devices eliminate the need for external switches and reduce integration complexity—while also aligning with the emerging Ethernet-based avionics stack.

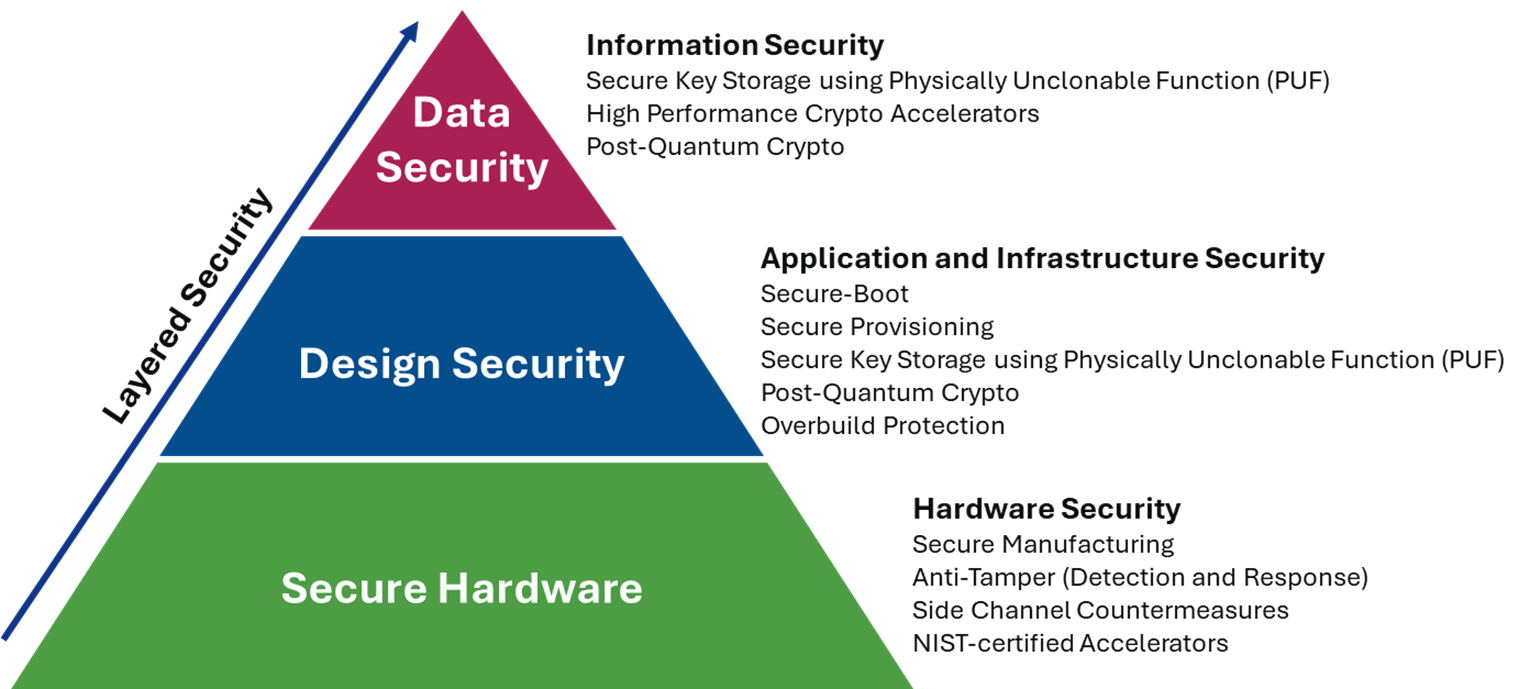

Defense-Grade Crypto and Anti-Tamper

Security is foundational—not a feature. That’s why the PIC64HX and PIC64-HPSC embed defense-grade cryptographic engines with a full suite of protection features:

- Robust anti-tamper mechanisms, including memory encryption, secure boot and tamper event response

- Side-channel and differential power analysis resistance, guarding against sophisticated reverse engineering and espionage threats

- Hardware support for root of trust, attestation and cryptographic key isolation

These features ensure not only data confidentiality and integrity, but also system survivability in contested environments.

Post-Quantum Crypto Readiness

The cryptographic future is post-quantum. Nation-state adversaries are already stockpiling encrypted data, waiting for the day quantum computers can break classical algorithms.

To address this, our latest 64-bit platforms incorporate hardware enablement for FIPS 203 (ML-KEM) and FIPS 204 (ML-DSA)—two of the leading NIST-selected PQC algorithms.

This gives developers a clear path to quantum-resistant system designs, years ahead of regulatory mandates, and with minimal performance penalty thanks to hardware offload support.

Designed for Certification and Longevity

Whether you’re targeting DO-254/DO-178C avionics certification, IEC 61508 for industrial safety or CCSDS and ECSS standards for space, both processors are designed with lifecycle support and certifiability in mind.

Their long-term availability, support for deterministic behavior and isolation of critical functions align well with safety processes and mission assurance programs.

Conclusion: Architecting the Future of Mission Critical Systems

The PIC64HX and PIC64-HPSC represent more than just a leap in performance—they are a redefinition of the embedded compute platform for the mission-critical age.

With a scalable 64-bit RISC-V architecture, built-in AI and TSN, robust isolation and security and native support for post-quantum cryptography, these devices give designers the tools they need to meet the next generation of requirements across air, space, defense and industry.

As the boundary between real-time control, AI analytics and secure communications continues to blur, Microchip’s PIC64 platforms are poised to be the backbone of next-generation mission systems—flexible enough for tomorrow’s innovations, and reliable enough for today’s missions.

For additional information:

- Please visit our PIC64HX and PIC64-HPSC webpages

- Schedule a call and be sure to indicate your product of interest

- For pricing and availability, contact Microchip Local Sales

- Connect with the author