Microchip SMC2100 CXL Controller: Benefits of Advanced RAS/ECC Capabilities for Your Data Center Solutions

Error correction in enterprise server memory is crucial for maintaining data integrity and system reliability. Downtime in data centers are very expensive mandating robust RAS capabilities on all deployments. Traditionally, SECDED (Single Error Correction Double Error Detection) Error Correction Code (ECC) has been the standard error correction methodology for Memory. CXL enables the ability to use different kinds of memories as well as re-use certain DRAM types such as DDR4 to enable total cost optimizations which necessitates more advanced techniques.

Introduction to SMC2100 CXL Controller with Advanced ECC

Our SMC2100 CXL controller utilizes sophisticated ECC correction methods like Chipkill™ to provide superior error correction capabilities compared to SECDED ECC. SMC2100 is the among the first CXL-based memory controllers on the market to implement Chipkill as part of its Reliability, Availability, Serviceability (RAS) suite—protecting against persistent and transient errors, multi-bit DRAM errors and even complete chip failures.

In this blog post, we will examine the features, benefits and applications of the SM2100 CXL controller advanced ECC technology. We will highlight how it minimizes errors in enterprise servers and data centers, thereby enhancing system reliability and uptime.

Why Choose SM2100 CXL Controller for Your Error Correction Needs?

In the era of Artificial Intelligence (AI), Machine Learning (ML) and High Performance Computing (HPC), there is a growing demand for efficient and reliable digital data storage and transmission between the CPU and DDR memory. Ensuring data integrity is critical, as data corruption can lead to severe system failures. Consequently, robust memory error detection and correction mechanisms are essential in enterprise data center architecture to maintain system reliability, cost efficiency, fault tolerance and lastly, data integrity.

Additionally, the latest CXL specifications have introduced metadata handling, which can be utilized for various purposes such as access control, data type tagging, cache coherency and memory tiering. Certain classes of enterprise servers employ advanced techniques to decode metadata and enhance performance. However, this introduces challenges for traditional SECDED ECC algorithms, which can only detect up to 2-bit errors and correct 1-bit errors, proving insufficient for current needs.

Advanced ECC detection and correction schemes implemented in SMC 2100 prevent data corruption and system crashes by identifying and correcting errors that occur while either being written or read from CXL attached DDR memory. For SMC 2100, DDR ECC schemes can be further classified into basic SECDED and Reed-Solomon based Chipkill as described below.

ECC Based on Traditional SECDED (Single Error Correction Double Error Detection)

SECDED is capable of detecting and correcting single-bit errors, as well as identifying double-bit errors. However, there is a potential risk of false decode in the event of a bit-flip. To enhance robustness, the implementation of advanced error correction technology like Chipkill is recommended. Chipkill algorithms extend the correction capability of a DRAM device, precluding uncorrectable errors at 0.1 per Mbit-year. Chipkill has even demonstrated a staggering 42-fold reduction in node failure rate compared to SECDED. In the era of big data, having advanced error correction algorithms is imperative.

Advanced ECC (Chipkill) based on Reed-Solomon Codes

Reed-Solomon codes are a form of error-correcting code extensively utilized in digital communication and storage systems. These codes process data in blocks, interpreting them as sets of finite-field elements known as symbols. Reed-Solomon codes are capable of detecting and correcting multiple symbol errors within a block of data. They are particularly effective for burst errors, where multiple bits in a burst are corrupted. Additionally, they can correct a specified number of erasures (errors at known locations) or a combination of errors and erasures which is the expected failure signatures from DRAM.

SMC2100 Advanced ECC technology, utilizing Reed-Solomon error correction, addresses errors at the symbol level. Each symbol consists of 16 bits, as demonstrated in the x4 DDR5 DRAM example provided below.

Figure 1. Symbol Placement for single x4 DDR5 device

In addition to SECDED, the SMC2100 supports five advanced ECC (Chipkill) modes, providing industry-leading error correction capabilities. These modes can be configured through our proprietary and intuitive Chiplink graphical user interface (GUI).

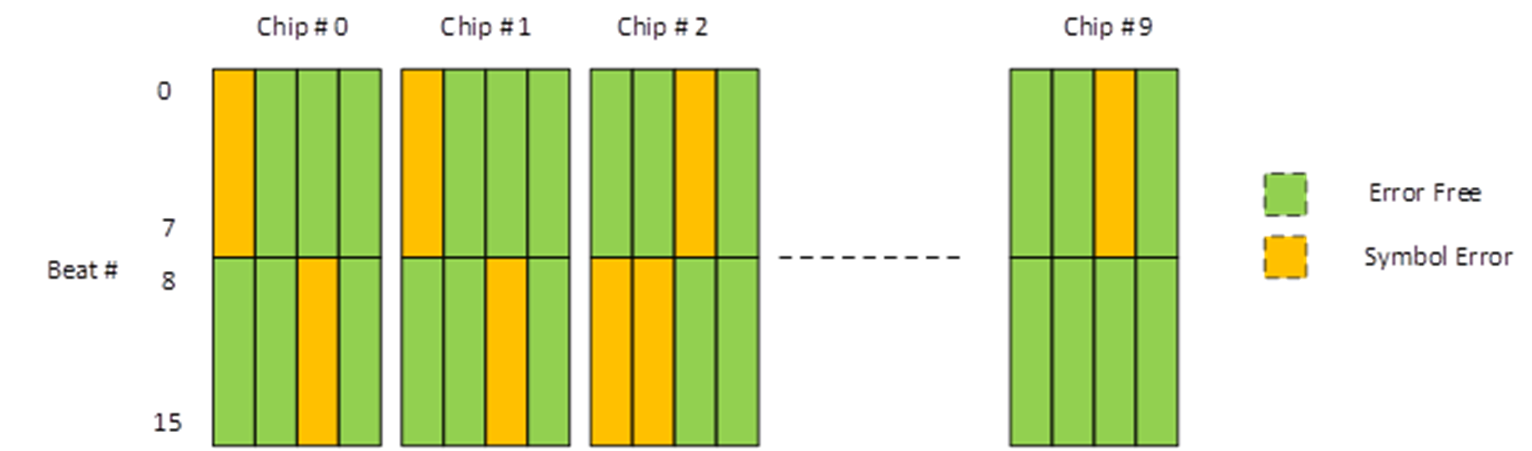

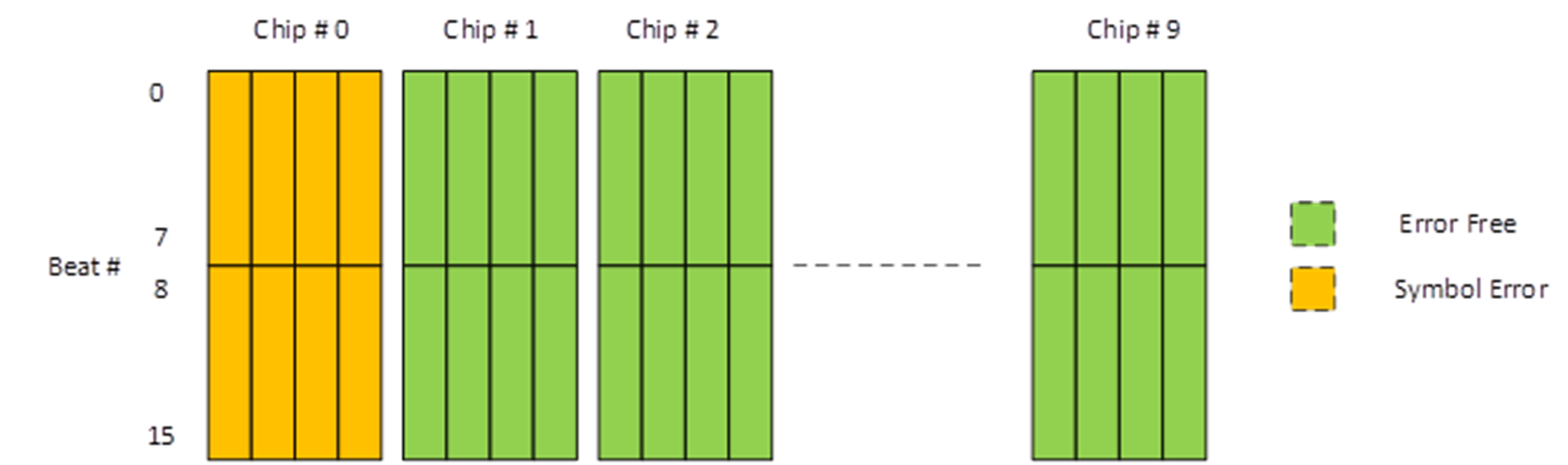

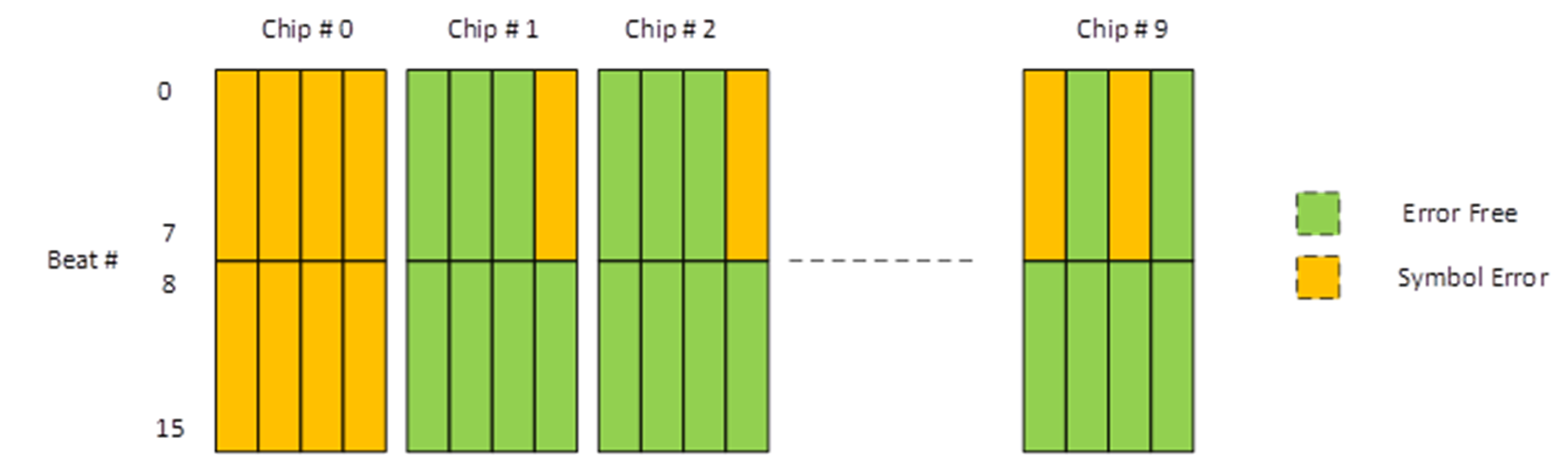

The figures below illustrate several examples of error correction using one of the advanced ECC Modes. For clarity, we have limited the scope to a single DDR5 DIMM sub-channel (4 x10 DRAM chips).

Figure 2. 8 random symbol errors – correctable

Figure 3. Chipkill (8 symbol errors within a single chip) – correctable

ddle">

Figure 4. Chipkill + 4 random errors – Correctable

Furthermore, the proprietary firmware of the SMC2100 enables users to monitor both correctable and uncorrectable errors. This makes SMC2100 an ideal solution for your data center and AI/ML/HPC applications.

Your Needs

- Data centers

- Cloud storage

- High-performance computing

- Enterprise storage

- Configurable ECC scheme based on your end application

Our Solutions

- Unparalleled performance: industry-leading error correction capabilities

- Flexibility: Advanced ECC correction capabilities which are configurable by the user using intuitive GUI. Allows the user to configure the number of symbol error threshold to trigger Chipkill

- Device Initiated PPR to extend the capabilities of SMC2100

Conclusion

In the era of AI, ML and HPC, robust memory error detection and correction mechanisms are essential to maintain system reliability, cost efficiency, fault tolerance and data integrity. Traditional ECC technology is unable to fulfil these requirements. Our SMC2100 advanced ECC technology plays a pivotal role in offering you industry-leading advanced error correction techniques.

Are you ready to enhance your CXL memory infrastructure with an advanced error correction technology? Reach out to us today to discover how the SMC2100 can address the specific requirements of your organization.