Fortify Your Edge Computing Solutions: Fault Tolerance in Microprocessors

Discover how fault-tolerant microprocessors transform mission-critical edge computing from fragile to robust. Learn how our PIC64-HPSC and PIC64HX MPUs set new standards for reliability, resilience and security in the most demanding environments.

The Rise of Intelligent Edge and Its Challenges

Edge computing is transforming industries by enabling real-time data processing and autonomous decision-making at the network’s periphery. As its applications expand from aerospace and defense into commercial sectors such as transportation and industrial automation, the demand for robust fault tolerance mechanisms has become paramount. Unlike centralized data centers, edge environments are decentralized and resource-constrained, making them more susceptible to faults and failures. The convergence of AI and edge computing amplifies both opportunities and risks, requiring innovative approaches to system robustness and reliability.

Imagine a medieval fortress built to withstand sieges, storms and sabotage. Its walls, moats and watchtowers are designed to not just repel attacks, but to keep the inhabitants safe no matter what comes their way. In mission-critical edge computing, a fault-tolerant CPU system is the digital fortress—protecting data, processes and decisions from unpredictable threats such as hardware failures, cosmic radiation and network disruptions. Just as every aspect of a fortress must be strong, edge computing systems must be strong at every layer. The microprocessor (MPU), as the core of any embedded computing system, stands at the very forefront of fault tolerance, ensuring that the entire digital fortress remains secure and operational even in the face of adversity.

Beyond TMR: What You’ll Learn About Fault-Tolerant Design

When it comes to fault-tolerant design techniques, many people default to Triple Modular Redundancy (TMR) as the go-to solution. While TMR is effective for error detection and correction, it is not always the most practical solution—especially in mission-critical environments where size, power and cost constraints are paramount. In many cases, TMR’s overhead makes it undesirable or even unfeasible. A truly robust fault-tolerant design is both comprehensive and holistic, employing the most suitable techniques at each stage and segment of the system.

Microchip’s PIC64-HPSC and PIC64HX microprocessors exemplify this advanced methodology. These devices implement multiple layers of fault tolerance, with different techniques tailored to specific parts of the MPU. Features such as Dual-Core Lockstep (DCLS), WorldGuard hardware partitioning, flexible core operating modes and dedicated system controllers enable these microprocessors to support mixed-criticality and safety-critical workloads while maintaining high performance and security.

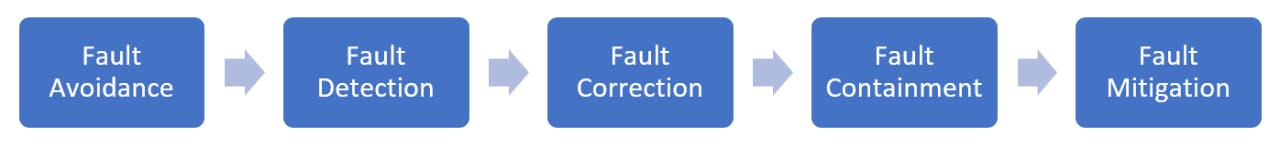

Fault-Tolerant Design: Five Sequential Steps for System Resilience

Both PIC64-HPSC and PIC64HX microprocessors feature unprecedented fault-tolerant design based on a logical sequence of five interconnected steps, each serving a distinct purpose in safeguarding system reliability:

- The process begins with fault avoidance, which aims to minimize the likelihood of faults occurring in the first place. The radiation-hardening design on the PIC64-HPSC MPUs is an example of avoiding Single-Event Errors for space environment.

- Next, fault detection techniques certify that any faults that arise are identified as early as possible, so they do not escalate into larger issues.

- Once detected, fault correction techniques such as Error Correction Coding (ECC) are in place to address and resolve these faults. All memories, cache and internal buses in PIC64-HPSC and PIC64HX MPUs are ECC-protected.

- The fourth step, fault containment, is crucial for isolating faults so they do not propagate and affect other parts of the system. WorldGuard hardware partitioning provides fine-grained isolation of code execution and data, preventing faults from spreading across predefined boundaries.

- Finally, fault mitigation provides mechanisms for the system to recover gracefully from failures or disruption, delivering continuous operation.

The fault-tolerant designs of our PIC64-HPSC and PIC64HX families integrate these five steps throughout the microprocessor’s architecture, implementation and manufacturing processes. This comprehensive strategy is essential for achieving robust, resilient systems while maintaining optimal space, weight, power and cost (SWaP-C).

For a deeper dive into these techniques and to learn how a highly fault-tolerant MPU can elevate and simplify the design of resilient compute systems for demanding applications—whether on land, in the air, at sea or in space, download our fault tolerance white papers for both the PIC64-HPSC and PIC64HX families. Login credentials are required; contact Microchip to request access.

Next Steps: Fortify Your Edge Computing Solutions

Ready to build your own fortress of reliability? Explore our PIC64-HPSC and PIC64HX microprocessors to see how their fault-tolerant features can transform your mission-critical edge applications. For more details and technical resources, visit our PIC64 product page. Connect with our team for expert guidance. Your mission-critical applications deserve nothing less than fortress-grade fault tolerance.