Building Secure HDMI® Video Pipelines With HDCP® Using PolarFire® FPGAs

A Practical, Low Power Approach to Deterministic HDMI® Receive Designs

Supporting HDCP®‑protected HDMI doesn’t have to complicate your design. This post outlines a straightforward, hardware‑based solution on PolarFire® FPGAs that helps engineers receive protected HDMI video reliably, while keeping power use low and designs easy to manage.

Why Secure HDMI Reception Matters

As video systems continue to evolve across professional AV, embedded vision, industrial automation and medical imaging, there is a growing requirement not only to ingest high‑resolution High-Definition Multimedia Interface (HDMI) video, but also to handle protected content securely and reliably.

Modern HDMI pipelines increasingly carry encrypted video streams that require HDCP (High‑bandwidth Digital Content Protection) to ensure that content is exchanged only between authorized source and sink devices. Without HDCP compliance, systems face interoperability gaps, an inability to display protected content and potential security exposure.

At the same time, embedded designers must preserve low latency, deterministic performance and power efficiency, particularly in always‑on or edge‑deployed systems. Balancing these constraints is not trivial—especially as resolutions move toward 4K and beyond.

This is where a hardware‑accelerated HDMI Receive (RX) architecture using our PolarFire FPGA technology becomes highly relevant.

Why This Solution Matters

Secure HDMI receive is now a baseline requirement across many embedded video platforms. Typical design challenges include supporting HDMI 2.0 bandwidths up to 4K60, managing HDCP authentication and encryption, minimizing power consumption and integrating cleanly with downstream video or vision pipelines.

Processor‑centric approaches often increase system complexity and power while introducing non‑deterministic timing behavior. By contrast, implementing HDMI and HDCP handling directly in FPGA hardware enables predictable latency, reduced software dependency and tighter system control—key requirements in industrial, medical and vision applications.

Solution Overview: HDMI RX With HDCP on PolarFire Family

PolarFire FPGA and PolarFire SoC FPGA devices combine low‑power nonvolatile architecture, high‑speed transceivers and a production‑qualified video IP portfolio to support secure HDMI receive designs.

At the front end, our HDMI RX IP terminates the HDMI protocol and converts incoming TMDS‑encoded streams into pixel‑aligned video and audio data in compliance with the HDMI 2.0 specification. The IP supports resolutions up to 3840 × 2160 at 60 Hz, multiple color formats (RGB and YUV) and bit depths up to 16 bits. Integrated FIFOs remove lane‑to‑lane skew, providing reliable reconstruction of the incoming stream.

For protected content, the CoreHDCPHDMIRX IP provides HDCP 2.3 receive functionality. Once authentication and key exchange are completed by the system, the core decrypts protected audio and video data entirely in hardware. This clean separation between HDCP control and the video data path simplifies integration while preserving content security.

Together, these blocks form a modular, scalable HDMI RX pipeline that maintains deterministic behavior while aligning with power‑ and lifecycle‑sensitive embedded systems.

HDMI RX + HDCP Capability Snapshot

Feature | PolarFire HDMI RX Solution |

HDMI Standard | HDMI 2.0 |

Maximum Resolution | Up to 3840 × 2160 @ 60 Hz |

Color Formats | RGB, YUV 4:2:2, YUV 4:4:4 |

Bit Depth | 8 / 10 / 12 / 16 bits |

Content Protection | HDCP 2.3 (Receive) |

Video Interfaces | Native Video, AXI4‑Stream |

Audio Support | HDMI Audio Packet Extraction |

Target Devices | PolarFire FPGA, PolarFire SoC FPGA |

Where This Fits

Industrial and Factory Automation

Fit for HMIs, operator panels and inspection systems that require reliable HDMI ingest, predictable latency and continuous operation in power‑constrained or fanless environments.

Embedded Vision and Edge Processing

Well-suited for systems ingesting HDMI camera or sensor output before FPGA‑based pre‑processing or edge inference, where deterministic pixel timing is often more important than raw throughput.

Medical Imaging and Visualization

Aligned with diagnostic and surgical display systems that prioritize signal integrity, content protection, long product lifecycles and stable platform availability.

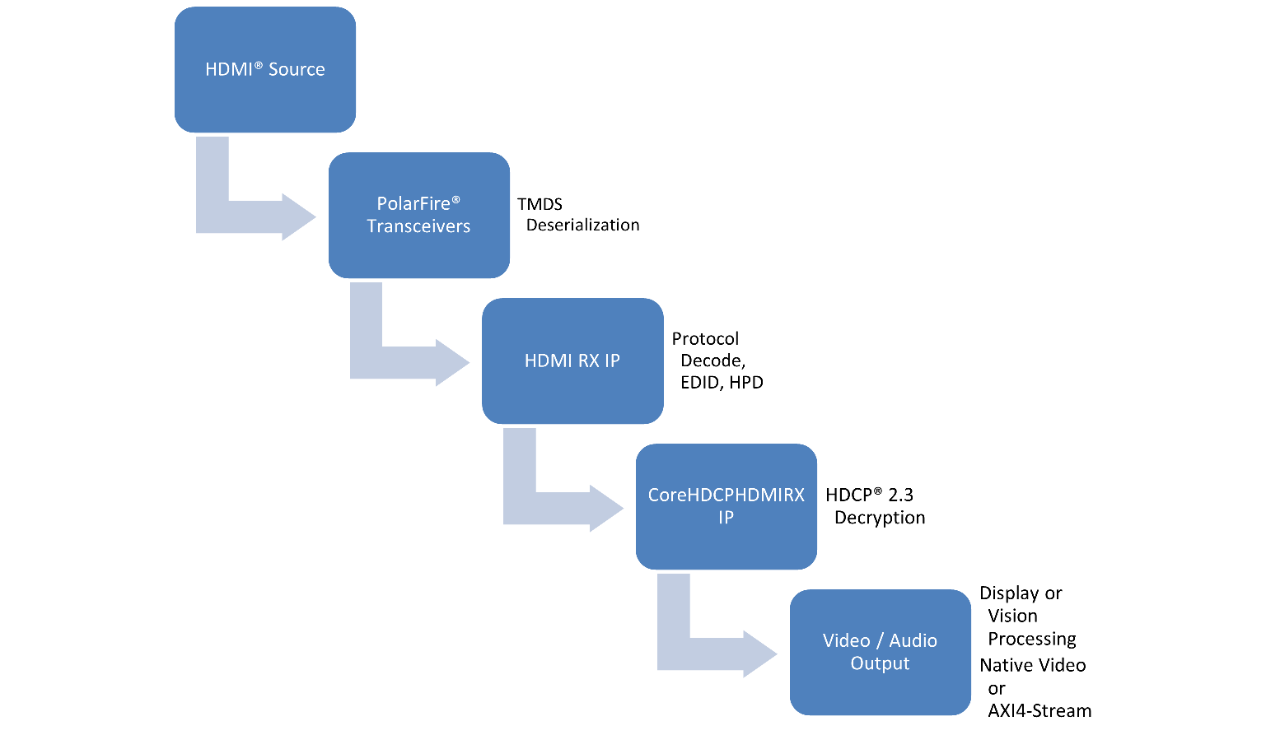

System Architecture Overview

A secure HDMI RX implementation on PolarFire FPGAs follows a clean, hardware‑centric data flow that keeps protocol handling, security and video transport fully deterministic.

HDMI RX With HDCP — Data Flow

At the physical layer, HDMI data enters the FPGA through PolarFire transceivers, where high‑speed serial streams are deserialized. The HDMI RX IP aligns lanes, removes skew and reconstructs pixel and audio data while managing HDMI‑specific control functions such as Hot Plug Detect (HPD) and EDID/DDC communication.

When protected content is present, the stream is routed through the CoreHDCPHDMIRX IP, which decrypts audio, video and auxiliary data in hardware before passing it downstream.

Implementation and Configuration Considerations

System integration is performed using the Libero® SoC Design Suite, with SmartDesign providing a visual block‑level environment for connecting IP, fabrics and clocks. HDMI RX IP configuration includes selecting pixel‑per‑clock operation, output interface type, supported color formats and EDID contents. Accurate EDID programming is essential to ensure HDMI sources correctly negotiate resolutions and formats.

The CoreHDCPHDMIRX IP is controlled via an APB3 interface, allowing the system to monitor decryption status and manage protected content paths. Treating HDCP as a first‑class architectural block—rather than a late‑stage feature—reduces integration risk and simplifies compliance.

From a system perspective, careful attention should be paid to clock‑domain crossings, FIFO sizing and buffering to accommodate resolution changes and worst‑case lane skew.

Technical Insight: Determinism, Latency and Bandwidth

HDMI reception places tight constraints on throughput and timing. TMDS decoding converts serialized data into parallel pixel streams, while FIFO‑based skew correction aligns HDMI lanes within specification limits. Handling these functions entirely in hardware removes variability associated with software‑driven pipelines.

HDCP decryption is likewise performed entirely in hardware, preventing protected content from traversing non‑deterministic CPU paths. This approach minimizes latency and jitter while maintaining strict security boundaries—an important requirement for real‑time vision, control and medical visualization systems.

Benefits of a Hardware‑Centric HDMI RX Architecture

Implementing HDMI RX and HDCP in FPGA hardware enables low‑power operation, deterministic performance and long‑term scalability. PolarFire FPGAs are optimized for low static and dynamic power, allowing secure HDMI video ingest in always‑on systems without excessive thermal overhead.

Pre‑validated IP and standardized interfaces simplify integration and speed development, while FPGA flexibility allows the architecture to evolve as video standards and application requirements change.

Why Microchip

Microchip’s FPGA and IP ecosystem supports secure video designs through a combination of low‑power PolarFire architecture, mature HDMI and HDCP IP, integrated design tools and long product lifecycles aligned with industrial and embedded markets. This enables engineers to build reliable, secure video pipelines with reduced complexity and predictable system behavior.

Conclusion

Secure HDMI receive has become a foundational requirement across modern embedded video platforms. By terminating HDMI and HDCP directly in PolarFire FPGA hardware, designers can achieve deterministic performance, power efficiency and compliance without over‑reliance on software.

This approach provides a scalable, engineering‑focused foundation for building secure video ingest pipelines—ready for today’s applications and adaptable for the future.