Enabling Faster Design and Easier Verification of Software Accelerators

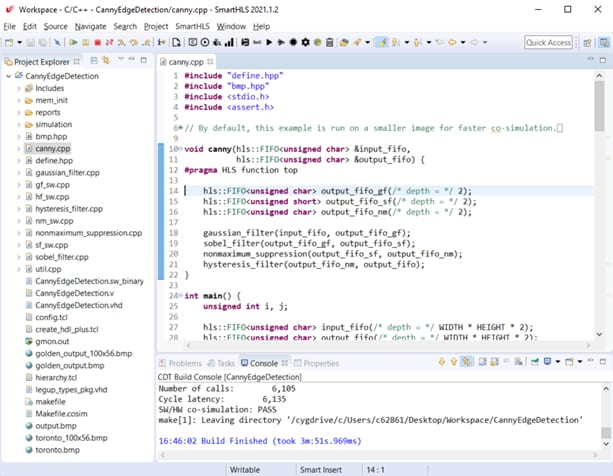

SmartHLS™ compiler software raises the FPGA design abstraction from traditional hardware description languages to C/C++ software, enabling shorter design time, easier verification and faster time to market for designs using our FPGAs.

In the SmartHLS compiler software, you can implement your design in C++ software and verify the functionality with software tests. Next, the SmartHLS high-level synthesis software compiles the C++ program into functionality-equivalent Verilog hardware modules. SmartHLS software can run co-simulation with ModelSim to verify cycle-accurate hardware behavior and confirm that the hardware functionality matches the software. SmartLHS software can generate hardware IP cores that you can integrate into a larger system using SmartDesign. It can also run Libero® software synthesis on the generated Verilog to determine the FPGA area and fMAX.

- Current Version

- Previous Versions

- Supported Platforms

We have integrated the SmartHLS compiler software into Libero SoC Design Suite versions 2022.3 and later.

Beginning with Libero SoC v2024.1, the SmartHLS Compiler is now included under the Libero software license, providing a more integrated and streamlined development experience.

SmartHLS v2022.2.1 Software (10/18/2022)

- SmartHLS v2022.2.1 Software Release Notes

- Download SmartHLS v2022.2.1 Software for Windows®

- MD5 Checksum: 65f534e554b570cffef00c271e2e5f29

- SHA256 Checksum: 1be2197aa0f9e1ca54d25b583e4c53d6267a7a4dcd211c59fe4640fff6963248

- Download SmartHLS v2022.2.1 Software for Linux®

- MD5 Checksum: b92bd3b45ba196ec82f8101e3ddf6e0e

- SHA256 Checksum: 8926fc365e308c6cc0d11ba473ec1b904a1621b9be04ca06c86c8f2726dc4944

SmartHLS v2022.2 Software (08/17/2022)

- SmartHLS v2022.2 Software Release Notes

- Download SmartHLS v2022.2 Software for Windows

- MD5 Checksum: b03444e7d86d38da799124c67ef7878b

- SHA256 Checksum: 68b29db89d860ceeb0a0287bed66599ccccca1d203544186f1829dd39b7afdde

- Download SmartHLS v2022.2 Software for Linux

- MD5 Checksum: 1a4fe79c4c0ceda10b4aa93a02b5a4f5

- SHA256 Checksum: 47b7d715678ea560d0fa6b9eb0fa46e00f58f23b137c4e9359113bad84854cdf

SmartHLS v2022.1.1 Software (06/16/2022)

- SmartHLS v2022.1.1 Software Release Notes

- Download SmartHLS v2022.1.1 Software for Windows

- MD5 Checksum: 853a96e66196f6c200af0d0bb4f346cc

- SHA256 Checksum: a640ebbd88f1498cdca7657b9edf94800e397d0653d73b0b34ffbfc376d1b621

- Download SmartHLS v2022.1.1 Software for Linux

- MD5 Checksum: 1922d2a536c9627763e317ed1933a356

- SHA256 Checksum: 6dbce34802197e4d6dd5d363d03364c29fa1b5cd9a5ddd03d6eb04eba2fcb2fd

SmartHLS v2022.1 Software (04/06/2022)

- SmartHLS v2022.1 Software Release Notes

- Download SmartHLS v2022.1 Software for Windows

- MD5 Checksum: d334644df1df809ea4f260b7c1684fc4

- SHA256 Checksum: 1ee7fc3968aa32c86bd749a3d60eb3e09ce9f587726dbce07e22ec2d7b6db645

- Download SmartHLS v2022.1 Software for Linux

- MD5 Checksum: 204d25a82a58529e8bc6c9ead99be994

- SHA256 Checksum: 08838f3ec0d10126a212d455fc600f4ef6a22b1862298685d6f41e40886dc09f

SmartHLS v2021.3.1 Software (01/31/2022)

- SmartHLS v2021.3.1 Software Release Notes

- Download SmartHLS v2021.3.1 Software for Windows

- MD5 Checksum: d979553d0e92253608312749ed7d6b14

- SHA256 Checksum: 0d967baf372b9a307d25473538353ffb0eb5e4ac1de97d9e94b9810dbd99481d

- Download SmartHLS v2021.3.1 Software for Linux

- MD5 Checksum: 30f421b5bb3ee02852ee85b6926c8ef5

- SHA256 Checksum: 035ed81ce8e28d994ab31cf133d6c30709ee6a636c733697ae379b0597179418

SmartHLS v2021.3 Software (12/09/2021)

- SmartHLS v2021.3 Software Release Notes

- Download SmartHLS v2021.3 Software for Windows

- MD5 Checksum: 24d72c2b9ac3314be7b3dddfac6b375d

- SHA256 Checksum: 30de541d26a28a96fa0afd3e7b4c8390c3f20cdd947b56fbdcdf16f7f5130c67

- Download SmartHLS v2021.3 Software for Linux

- MD5 Checksum: 31133e72b69b2a7bfbe6091703e39122

- SHA256 Checksum: fbddc199bc450a109b9727f296052044b4d800092533bbab442b34cb89f425f4

SmartHLS v2021.2.1 Software (09/28/2021)

- SmartHLS v2021.2.1 Software Release Notes

- Download SmartHLS v2021.2.1 Software for Windows

- Download SmartHLS v2021.2.1 Software for Linux

SmartHLS v2021.2 Software (08/09/2021)

- SmartHLS v2021.2 Software Release Notes

- Download SmartHLS v2021.2 Software for Windows

- Download SmartHLS v2021.2 Software for Linux

Important Notes:

- SmartHLS v2021.2 software is integrated with Libero® SoC Design Suite v2021.2

- We recommend using the Libero SoC Design Suite v2021.2 release along with the SmartHLS v2021.2 stand-alone software

- SmartHLS v2021.2 software release requires a free stand-alone license

- Refer to this web page to learn how to generate and install a license

Supported Devices

- PolarFire® FPGAs

- SmartFusion® 2 FPGAs

- IGLOO® 2 FPGAs

- User Guides

- Training