# USB 2.0 Hi-Speed Graphics Controller with VGA, HDMI/DVI, and Digital RGB Interfaces

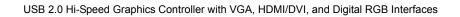

**UFX6000**

## **PRODUCT FEATURES**

#### Databook

### **Highlights**

- Single-Chip Hi-Speed USB 2.0 Graphics Adapter

- USB 2.0 Device Controller with Integrated USB 2.0 PHY

- Highly Efficient Compression Algorithm

- HDMI/DVI Display Connectivity via Integrated HDMI/DVI Controller/PHY

- VGA Display Connectivity via Integrated Video DAC

- Support for External Display Interface IC's via Digital RGB Interface

- High Performance DDR2 SDRAM Controller with Integrated DDR2 PHY

#### **Target Applications**

- USB to Video Adapters

- Docking Stations, USB Port Replicators

- Thin Clients

- USB Monitors and Projectors

- Embedded Systems

#### **Features**

- USB 2.0 Device Controller

- Fully compliant with Universal Serial Bus Specification Revision 2.0

- Operates in HS (480 Mbps) mode

- Supports Control, Bulk-Out, and Interrupt-In endpoints

- Supports vendor specific commands

- Integrated USB 2.0 PHY

- Integrated USB termination pull-up/pull-down resistors

- Short circuit protection of USB differential signals

- Graphics Subsystem

- Integrated HDMI/DVI Controller and PHY

- Complies with DVI specification v1.0

- Complies with HDMI specification v1.3

- S/PDIF and I<sup>2</sup>S inputs for HDMI audio (2-channel uncompressed PCM)

- Master I<sup>2</sup>C interface for DDC connection

- Integrated Triple 10-bit Video DAC with VGA output

- Digital RGB Interface

- 12/15-bit double data rate digital RGB

24-bit single data rate digital RGB

- Supports up to 2048x1152 (QWXGA) with 32-bit color

- 8-bit and 16-bit color support

- Supports display cloning and extending

- Standard and wide screen aspect ratios

- Complies with VESA auto display identification

- Gamma correction

- Color Look-Up Table (CLUT)

- Triple-buffered animations

- Graphics Engine

- Optimized algorithms for static and dynamic content

- I<sup>2</sup>C controller

- DDR2 SDRAM Controller

- 16-bit data bus, 13-bit address bus

- JEDEC DDR2 compliant (JESD79-2E)

- Integrated DDR2 SDRAM PHY

- Power

- Reduced power operating modes

- Supports bus-powered and self-powered operation

- Miscellaneous Features

- Optional EEPROM controller

- IEEE 1149.1 (JTAG) boundary scan TAP controller

- Software

- Microsoft Windows® XP/Vista/7 drivers

- Packaging & Environmental

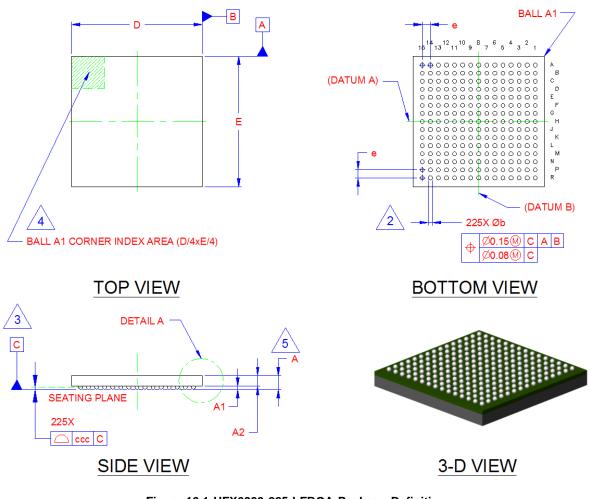

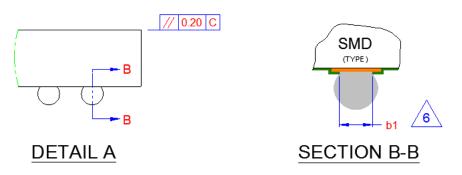

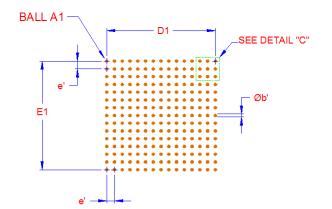

- 225-ball LFBGA, lead-free RoHS compliant package

- Commercial temperature range (0°C to +70°C)

#### Order Number:

UFX6000-VE FOR 225-BALL LFBGA Pb-FREE ROHS COMPLIANT PACKAGE (0 TO +70°C TEMP RANGE)

This product meets the halogen maximum concentration values per IEC61249-2-21 For RoHS compliance and environmental information, please visit www.smsc.com/rohs

80 ARKAY DRIVE, HAUPPAUGE, NY 11788 (631) 435-6000, FAX (631) 273-3123

#### Copyright © 2013 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

# **Table of Contents**

| -          | oter 1 General Terms and Conventions                        |    |

|------------|-------------------------------------------------------------|----|

| 1.1        | General Terms                                               |    |

| 1.2        | Register Nomenclature                                       | 16 |

| Char       | oter 2 Overview                                             |    |

| 2.1        | USB Controllers and PHYs                                    | 17 |

| 2.2        | Graphics Engine (GPH)                                       |    |

| 2.2        | DDR2 Controller and PHY                                     |    |

| 2.3<br>2.4 |                                                             |    |

|            | Display Controller (DISP)                                   |    |

| 2.5        |                                                             |    |

| 2.6        | System PLL (SYS)                                            |    |

| 2.7        | Video DAC (DAC)                                             |    |

| 2.8        | Audio Controller (AUDIO)                                    |    |

| 2.9        | HDMI/DVI Controller                                         |    |

| 2.10       | I2C                                                         |    |

| 2.11       | EEPROM                                                      |    |

| 2.12       | TAP Controller                                              | 21 |

| 2.13       | Performance                                                 | 21 |

| 2.14       | System Memory Map                                           | 22 |

|            |                                                             |    |

|            | oter 3 Pin Description and Configuration                    |    |

| 3.1        | Pin Assignments                                             |    |

| 3.2        | Buffer Types                                                | 43 |

|            |                                                             |    |

| Char       | oter 4 USB Controller                                       |    |

| 4.1        | Overview                                                    | 44 |

| 4.2        | USB Control Endpoint.                                       | 44 |

|            | 4.2.1 USB Vendor Commands                                   | 44 |

| 4.3        | USB Bulk Out Endpoint                                       | 46 |

| 4.4        | USB Interrupt Endpoint.                                     | 47 |

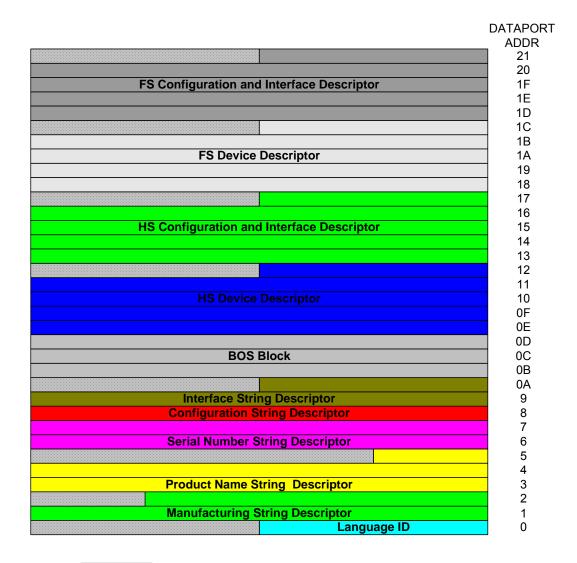

| 4.5        | USB Descriptors                                             |    |

|            | 4.5.1 USB Descriptors - UFX6000                             |    |

| 4.6        | Control and Status Registers                                |    |

|            | 4.6.1 USB Configuration Register (USB_CFG)                  |    |

|            | 4.6.2 USB Interrupt Endpoint Status Register (USB_INT_STS). |    |

|            | 4.6.3 USB Interrupt Endpoint Control Register (USB INT_CTL) |    |

|            |                                                             |    |

| Char       | oter 5 Clocks and Power Management                          |    |

| 5.1        | Overview                                                    | 63 |

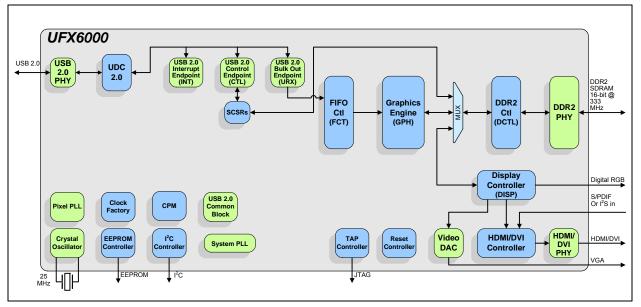

| 5.2        | Power States                                                |    |

| 0.2        | 5.2.1 Power State Definitions                               |    |

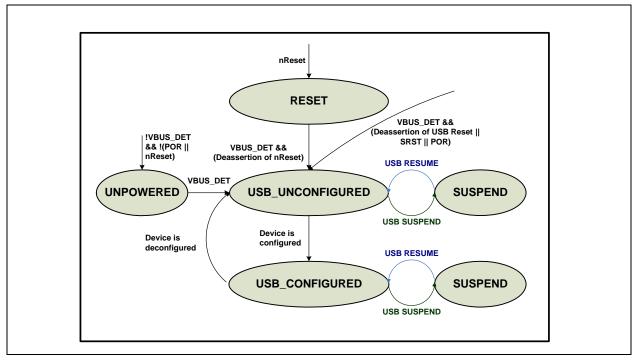

|            | 5.2.2 VBUS Detection.                                       |    |

|            |                                                             |    |

| - 0        | 5.2.3 Power State Mapping Tables                            |    |

| 5.3        |                                                             |    |

| 5.4        | Pixel and System PLLs.                                      |    |

|            | 5.4.1 Overview                                              |    |

|            | 5.4.2 PLL Programming                                       |    |

|            | 5.4.3 PLL Programming Examples                              |    |

|            | 5.4.4 DDR2 Clock Frequency Considerations                   |    |

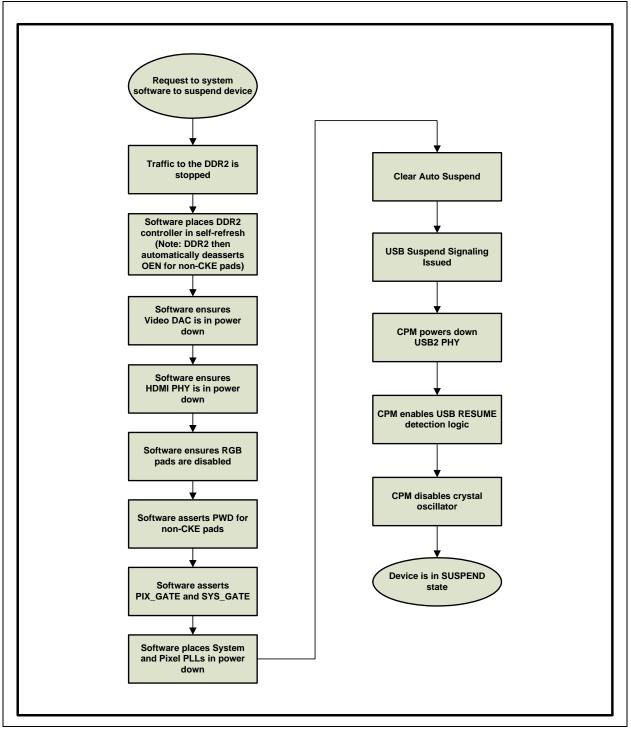

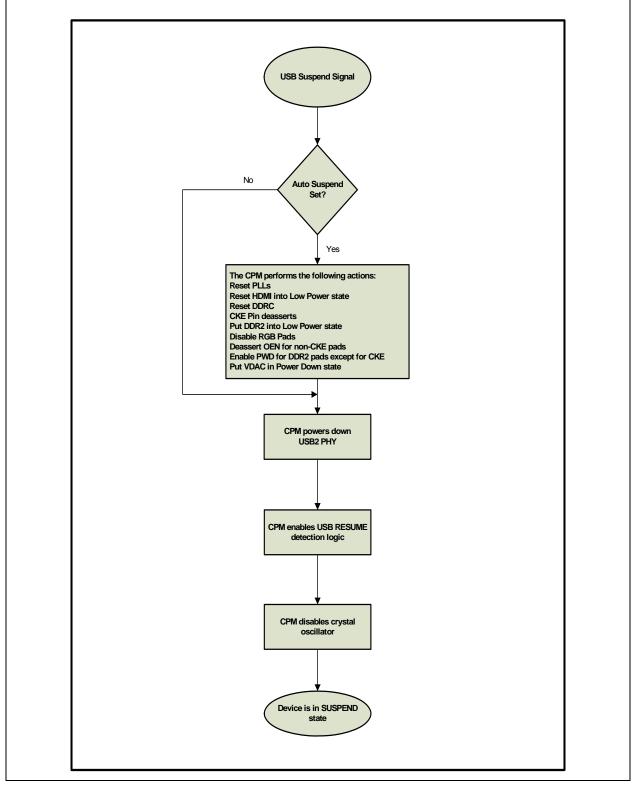

| 5.5        | USB Suspend                                                 | 70 |

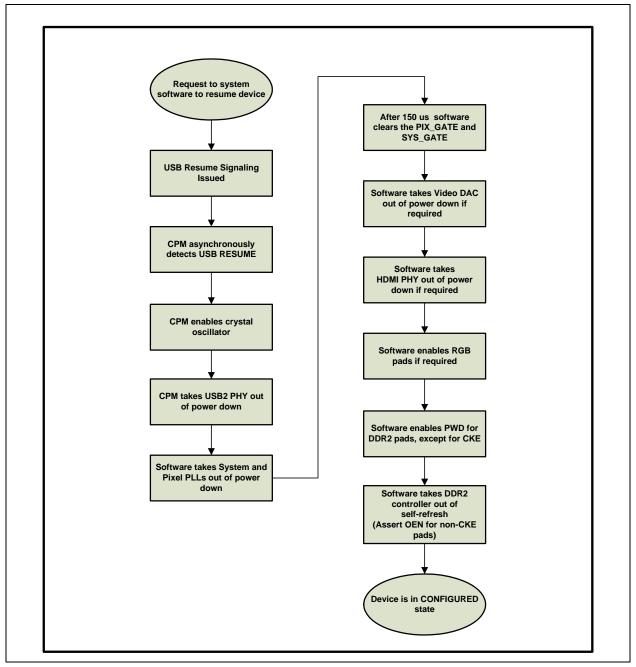

| 5.6        | USB Resume                                                  | 73 |

| 5.7                     | LPM Su  | Jpport                                                         | ŀ |

|-------------------------|---------|----------------------------------------------------------------|---|

| 5.8                     |         |                                                                |   |

| 5.9                     |         | and Status Registers                                           |   |

|                         | 5.9.1   | Pixel Clock PLL Control Register (PIX_PLL_CTL)                 | 3 |

|                         | 5.9.2   | Pixel Clock PLL Stage 0 Configuration Register (PIX_PLL0_CFG)  | 3 |

|                         | 5.9.3   | Pixel Clock PLL Stage 1 Configuration Register (PIX_PLL1_CFG)  | ) |

|                         | 5.9.4   | System Clock PLL Control Register (SYS_PLL_CTL)                |   |

|                         | 5.9.5   | System Clock PLL Stage 0 Configuration Register (SYS_PLL0_CFG) |   |

|                         | 5.9.6   | System Clock PLL Stage 1 Configuration Register (SYS_PLL1_CFG) |   |

|                         | 5.9.7   | CPM Control Register (CPM_CTL)                                 |   |

|                         | 0.0.1   |                                                                | - |

| Cha                     |         | Reset Generator                                                |   |

| 6.1                     | Descrip | tion                                                           | 5 |

| Cha                     | pter 7  | Memory Controller                                              |   |

| 7.1                     |         | ew                                                             | , |

| 7.2                     |         | tion of Controller Functions                                   |   |

|                         | 7.2.1   | Address Mapper                                                 |   |

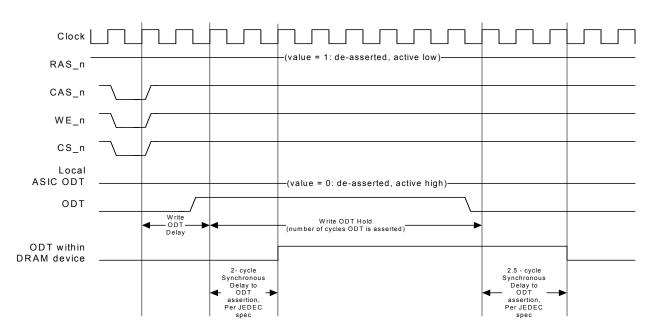

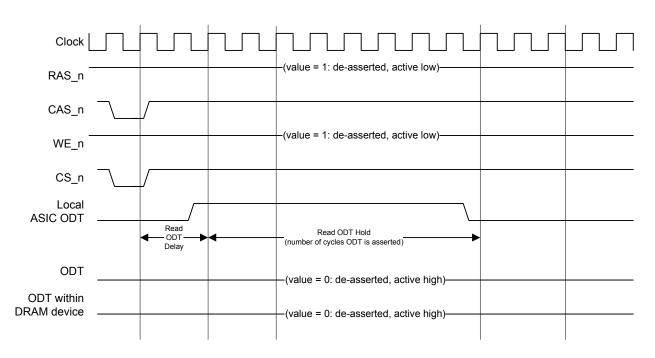

|                         | 7.2.2   | ODT Controls                                                   |   |

|                         | 7.2.3   | Refresh Controls                                               |   |

|                         | 7.2.4   | DLL Calibration                                                |   |

|                         | 7.2.5   | Power Saving Features                                          |   |

|                         | 7.2.6   | DRAM Initialization Sequence                                   |   |

| 7.3                     |         | Controller Configuration                                       |   |

| 1.0                     | 7.3.1   | Auto Initialization                                            |   |

|                         | 7.3.2   | Configuration Example                                          |   |

| 7.4                     |         | ng Modes                                                       |   |

| <i>י</i> . <del>-</del> | 7.4.1   | Moving To Power Down                                           |   |

|                         | 7.4.2   | Moving To Self Refresh                                         |   |

|                         | 7.4.3   | List of Dynamic Registers                                      |   |

|                         | 7.4.4   | Refresh Related Signals                                        |   |

|                         | 7.4.4   | Changing Clock Frequencies                                     |   |

| 7 5                     |         |                                                                |   |

| 7.5                     |         | and Status Registers                                           |   |

|                         | 7.5.1   | DDR2 Dynamic Register (DDR_DYN_REG)                            |   |

|                         | 7.5.2   | DDR2 Bank/CS Address Mapping Register (DDR_AD_MAP_BA_CS)       |   |

|                         | 7.5.3   | DDR2 Column Address Mapping Register (DDR_AD_MAP_COL)          |   |

|                         | 7.5.4   | DDR2 Row Address Mapping Register (DDR_AD_MAP_ROW)             |   |

|                         | 7.5.5   | DDR2 Timing Register 0 (DDR_TIMING_0) 107                      |   |

|                         | 7.5.6   | DDR2 Timing Register 1 (DDR_TIMING_1) 108                      |   |

|                         | 7.5.7   | DDR2 Timing Register 2 (DDR_TIMING_2) 109                      |   |

|                         | 7.5.8   | DDR2 Timing Register 3 (DDR_TIMING_3) 110                      |   |

|                         | 7.5.9   | DDR2 Timing Register 4 (DDR_TIMING_4)                          |   |

|                         | 7.5.10  | DDR2 Refresh Register (DDR_REFRESH)                            |   |

|                         | 7.5.11  | DDR2 Control Register 0 (DDR_CONTROL_0)                        |   |

|                         | 7.5.12  | DDR2 Control Register 1 (DDR_CONTROL_1)                        |   |

|                         | 7.5.13  | DDR2 Control Register 2 (DDR_CONTROL_2) 116                    |   |

|                         | 7.5.14  | DDR2 Control Register 3 (DDR_CONTROL_3) 117                    |   |

|                         | 7.5.15  | DDR2 Control Register 4 (DDR_CONTROL_4) 118                    |   |

|                         | 7.5.16  | DDR2 Control Register 5 (DDR_CONTROL_5) 119                    |   |

|                         | 7.5.17  | DDR2 Control Register 6 (DDR_CONTROL_6) 120                    |   |

|                         | 7.5.18  | DDR2 Control Register 7 (DDR_CONTROL_7) 121                    |   |

|                         | 7.5.19  | DDR2 Control Register 8 (DDR_CONTROL_8) 122                    |   |

|                         | 7.5.20  | DDR2 Control Register 9 (DDR_CONTROL_9) 123                    |   |

|                         | 7.5.21  | DDR2 Control Register 10 (DDR_CONTROL_10) 124                  |   |

|                         | 7.5.22  | DDR2 Control Register 11 (DDR_CONTROL_11) 125                  | 5 |

| 7.5.23 | DDR2 Control Register 12 (DDR_CONTROL_12)    | . 126 |

|--------|----------------------------------------------|-------|

| 7.5.24 | DDR2 Control Register 13 (DDR_CONTROL_13)    | . 127 |

| 7.5.25 | DDR2 PHY Control Register 0 (DDR_PHY_CTL_0)  | . 128 |

| 7.5.26 | DDR2 PHY Control Register 1 (DDR_PHY_CTL_1). | . 130 |

| 7.5.27 | DDR2 PHY Debug Register 0 (DDR_PHY_DEBUG_0)  | . 131 |

| 7.5.28 | DDR2 PHY Debug Register 1 (DDR_PHY_DEBUG_1)  | . 132 |

| 7.5.29 | DDR2 PHY Debug Register 2 (DDR_PHY_DEBUG_2)  | . 133 |

| 7.5.30 | DDR2 PHY Debug Register 3 (DDR_PHY_DEBUG_3)  | . 134 |

| 7.5.31 | DDR2 PHY Debug Register 4 (DDR_PHY_DEBUG_4)  | . 135 |

| 7.5.32 | DDR2 PHY Debug Register 5 (DDR_PHY_DEBUG_5)  | . 136 |

| 7.5.33 | DDR2 PHY Debug Register 6 (DDR_PHY_DEBUG_6)  | . 137 |

| 7.5.34 | DDR2 PHY Debug Register 7 (DDR_PHY_DEBUG_7)  | . 138 |

| 7.5.35 | DDR2 PHY Debug Register 8 (DDR_PHY_DEBUG_8)  | . 139 |

|        |                                              |       |

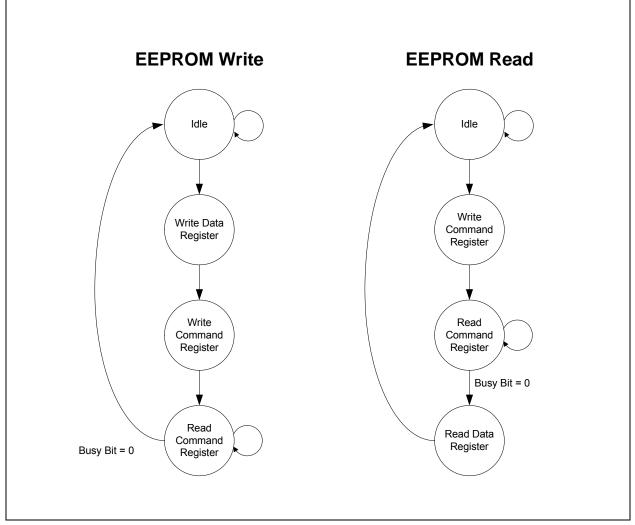

## Chapter 8 EEPROM

| 8.1 | Descripti | on                                                      | 140 |

|-----|-----------|---------------------------------------------------------|-----|

|     |           | Command Register Format                                 |     |

|     | 8.1.2     | Data Register Format                                    | 141 |

| 8.2 | EEPRON    | / Format                                                | 141 |

| 8.3 | EEPRON    | / Defaults                                              | 146 |

| 8.4 | Customiz  | zed Operation Without EEPROM                            | 147 |

|     | 8.4.1     | Initialization of SCSR Elements in Lieu of EEPROM Load  | 147 |

|     | 8.4.2     | Attribute Register Initialization                       | 147 |

|     | 8.4.3     | Descriptor RAM Initialization                           | 148 |

|     | 8.4.4     | Enable Descriptor RAM and Attribute Registers as Source | 150 |

|     | 8.4.5     | Inhibit Reset of Select SCSR Elements.                  | 150 |

| 8.5 | Control a | Ind Status Registers                                    | 151 |

|     | 8.5.1     | EEPROM Command Register (E2P_CMD).                      | 152 |

|     | 8.5.2     | EEPROM Data Register (E2P_DATA)                         | 155 |

# Chapter 9 HDMI

| 9.1 | Overview | 156 |

|-----|----------|-----|

|-----|----------|-----|

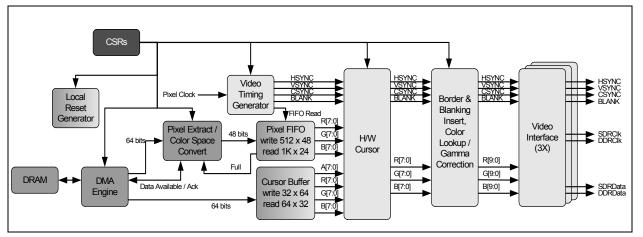

## **Chapter 10 Display Controller**

| 10.1 | Introduct | ion                                                       |

|------|-----------|-----------------------------------------------------------|

| 10.2 | Block Dia | agram                                                     |

| 10.3 | Configur  | ation                                                     |

|      | 10.3.1    | Controller Reset / Enable / Status                        |

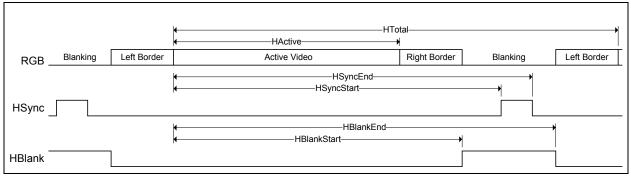

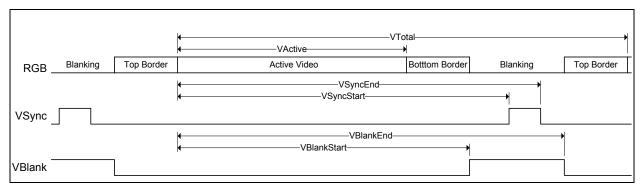

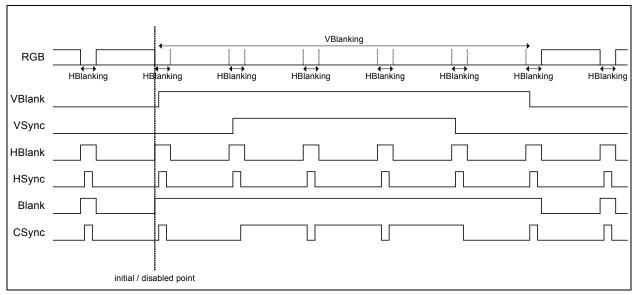

|      | 10.3.2    | Horizontal and Vertical Timing Configuration              |

|      | 10.3.3    | Display Blanking                                          |

|      | 10.3.4    | Display Frame Buffer Processing                           |

|      | 10.3.5    | Display Data Interpretation                               |

|      | 10.3.6    | Display Cursor                                            |

|      | 10.3.7    | Combining Cursor and Display Frame Data                   |

|      | 10.3.8    | Color Lookup/Gamma Correction Via The Color Lookup Table  |

|      | 10.3.9    | Border and Blanking Insert, Color Lookup/Gamma Correction |

|      | 10.3.10   | Interface Control                                         |

| 10.4 | Display ( | Controller Programming Outline                            |

|      | 10.4.1    | Initialization                                            |

|      | 10.4.2    | System Operation                                          |

| 10.5 | Control a | and Status Registers                                      |

|      | 10.5.1    | Display Control Register (DISPLAY_CTRL) 172               |

|      | 10.5.2    | Display Status Register (DISPLAY_STATUS)                  |

|      | 10.5.3    | Display Horizontal Size Register (DISPLAY_H_SIZE) 176     |

|      | 10.5.4    | Display Horizontal Blank Register (DISPLAY_H_BLANK)       |

| 10.5.5  | Display Horizontal Sync Register (DISPLAY_H_SYNC) 178                      |

|---------|----------------------------------------------------------------------------|

| 10.5.6  | Display Vertical Size Register (DISPLAY_V_SIZE)                            |

| 10.5.7  | Display Vertical Blank Register (DISPLAY_V_BLANK)                          |

| 10.5.8  | Display Vertical Sync Register (DISPLAY_V_SYNC)                            |

| 10.5.9  | Display Frame Buffer Base Address Register (DISPLAY_FRAME_BASE_ADDR) 182   |

| 10.5.10 | Display Border Color Register (DISPLAY_BORDER_COLOR)                       |

| 10.5.11 | Display Frame Buffer Length Register (DISPLAY_FRAME_LEN)                   |

| 10.5.12 | Display Frame Base Address Changed Count Register                          |

|         | (DISPLAY_FRAME_BASE_ADDR_CHANGED_CNT)185                                   |

| 10.5.13 | Display Interface Control 0 Register (DISPLAY_INTERFACE_CTRL_0) 186        |

| 10.5.14 | Display Interface Control 1 Register (DISPLAY_INTERFACE_CTRL_1) 187        |

| 10.5.15 | Display Interface Control 2 Register (DISPLAY_INTERFACE_CTRL_2) 188        |

| 10.5.16 | Display Cursor Control Register (DISPLAY_CURSOR_CTRL)                      |

| 10.5.17 | Display Cursor Status Register (DISPLAY_CURSOR_STATUS) 192                 |

| 10.5.18 | Display Cursor Base Address Register (DISPLAY_CURSOR_BASE_ADDR) 193        |

| 10.5.19 | Display Cursor Current Base Address Register                               |

|         | (DISPLAY_CURSOR_CUR_BASE_ADDR)194                                          |

| 10.5.20 |                                                                            |

| 10.5.21 | Display Cursor Current Position Register (DISPLAY_CURSOR_CUR_POSITION) 196 |

| 10.5.22 | Display Cursor Color 0 Register (DISPLAY_CURSOR_COLOR_0) 197               |

| 10.5.23 | Display Cursor Current Color 0 Register (DISPLAY_CURSOR_CUR_COLOR_0) 198   |

| 10.5.24 | Display Cursor Color 1 Register (DISPLAY_CURSOR_COLOR_1) 199               |

| 10.5.25 | Display Cursor Current Color 1 Register (DISPLAY_CURSOR_CUR_COLOR_1) 200   |

| 10.5.26 | Display Cursor Color 2 Register (DISPLAY_CURSOR_COLOR_2) 201               |

| 10.5.27 | Display Cursor Current Color 2 Register (DISPLAY_CURSOR_CUR_COLOR_2) 202   |

| 10.5.28 | Display Cursor Color 3 Register (DISPLAY_CURSOR_COLOR_3) 203               |

| 10.5.29 | Display Cursor Current Color 3 Register (DISPLAY_CURSOR_CUR_COLOR_3) 204   |

| 10.5.30 | Display Color Lookup Table (DISPLAY_CLUT)                                  |

### **Chapter 11 Graphics Engine**

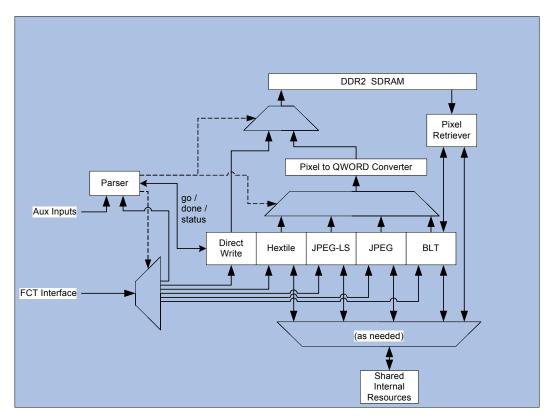

| 11.1 | Overviev  | V                                   | 206 |

|------|-----------|-------------------------------------|-----|

| 11.2 | FIFO (FC  | CT) Interface                       | 207 |

| 11.3 | Commar    | nd Parser                           | 207 |

|      | 11.3.1    | Error Checking and Handling         | 207 |

|      | 11.3.2    | Aborting Command                    | 208 |

|      | 11.3.3    | Graphics Engine Commands.           | 208 |

|      | 11.3.4    | Command Parser Implemented Commands | 208 |

| 11.4 | Direct R/ | AM Write Co-processor               | 210 |

|      | 11.4.1    | Error Checking and Handling         | 211 |

|      | 11.4.2    | Aborting Command                    | 211 |

| 11.5 | BLT Co-   | processor                           | 211 |

|      | 11.5.1    | Error Checking and Handling         | 216 |

|      | 11.5.2    | Aborting Command                    |     |

|      | 11.5.3    | Writing to Display Frame Buffer.    | 217 |

|      | 11.5.4    | DRAW_FILLED_RECTANGLE               | 217 |

|      | 11.5.5    | DRAW_RAW_RECTANGLE                  | 217 |

|      | 11.5.6    | ROP_RECTANGLE                       | 218 |

|      | 11.5.7    | ROP_RAW_RECTANGLE                   | 219 |

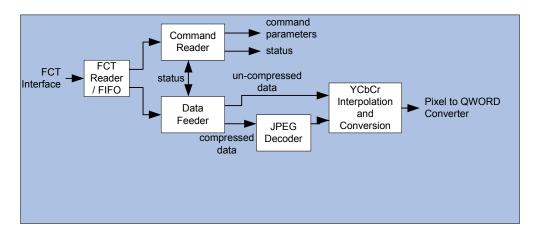

| 11.6 | JPEG Co   | p-processor                         | 220 |

|      | 11.6.1    | Error Checking and Handling         | 223 |

|      | 11.6.2    | Aborting Command                    | 223 |

|      | 11.6.3    | Block Diagram                       | 223 |

|      | 11.6.4    | FCT Reader / FIFO                   | 224 |

|      | 11.6.5    | Command Reader                      | 224 |

|      | 11.6.6    | Data Feeder                         | 224 |

|       | 11.6.7     | JPEG Decoder                                                         | . 224 |

|-------|------------|----------------------------------------------------------------------|-------|

|       | 11.6.8     | YCbCr Interpolation and Conversion.                                  | . 225 |

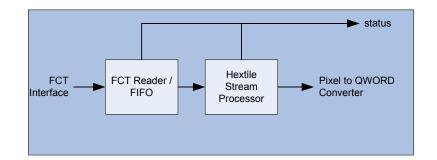

| 11.7  | Hextile C  | Co-processor                                                         | . 225 |

|       | 11.7.1     | Error Checking and Handling                                          | . 226 |

|       | 11.7.2     | Aborting Command                                                     | . 227 |

|       | 11.7.3     | Block Diagram                                                        | . 227 |

|       | 11.7.4     | FCT Reader / FIFO                                                    | . 228 |

|       | 11.7.5     | Hextile Stream Processor                                             | . 228 |

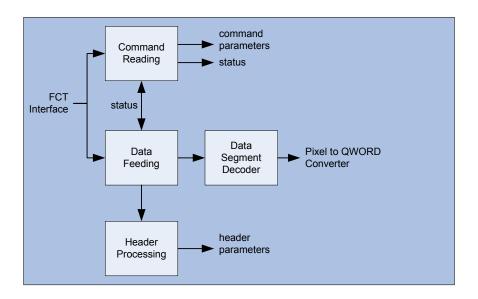

| 11.8  | JPEG-LS    | S Co-processor                                                       |       |

|       | 11.8.1     | Error Checking and Handling                                          | . 231 |

|       | 11.8.2     | Aborting Command                                                     | . 231 |

|       | 11.8.3     | Block Diagram                                                        | . 232 |

|       | 11.8.4     | Command Reading                                                      | . 232 |

|       | 11.8.5     | Data Feeding                                                         | . 232 |

|       | 11.8.6     | Header Processing                                                    | . 232 |

|       | 11.8.7     | Data Segment Decoder                                                 | . 233 |

|       | 11.8.8     | Writing to Display Frame Buffer.                                     | . 234 |

| 11.9  | General    | Error Checking and Handling                                          | . 234 |

| 11.10 | Pixel Re   | triever                                                              | . 234 |

|       | 11.10.1    | Pixel Retrieving                                                     | . 234 |

|       | 11.10.2    | Pixel Reading                                                        | . 234 |

|       | 11.10.3    | Pixel Color Data.                                                    | . 234 |

|       | 11.10.4    | Error Checking and Handling                                          | . 234 |

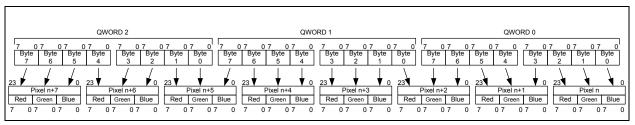

| 11.11 | Pixel to ( | QWORD Converter                                                      | . 235 |

|       | 11.11.1    | Memory Address                                                       | . 235 |

|       | 11.11.2    | Pixel Color Data.                                                    | . 235 |

| 11.12 | Control a  | and Status Registers                                                 | . 235 |

|       | 11.12.1    | Graphic Engine Control Register (GE_CTRL)                            | . 236 |

|       | 11.12.2    | Graphic Engine Command Status Register (GE_CMD_STATUS)               | 237   |

|       | 11.12.3    | Graphic Engine Command Info Register (GE_CMD_INFO)                   |       |

|       | 11.12.4    | Graphic Engine Command Length Register (GE_CMD_LEN)                  |       |

|       | 11.12.5    | Graphic Engine Command Offset Register (GE_CMD_OFFSET)               |       |

|       | 11.12.6    | Graphic Engine Previous Command Info Register (GE_PREV_CMD_INFO)     |       |

|       | 11.12.7    |                                                                      |       |

|       | 11.12.8    | Graphic Engine Previous Command Offset Register (GE_PREV_CMD_OFFSET) |       |

|       |            | Graphic Engine Chroma Key High Register (GE_CHROMA_KEY_HIGH)         |       |

|       | 11.12.10   | ) Graphic Engine Chroma Key Low Register (GE_CHROMA_KEY_LOW)         | . 246 |

| 11.13 | Error Re   | covery                                                               | . 247 |

|       | 11.13.1    | USB 3-Strike Error Recovery.                                         | . 247 |

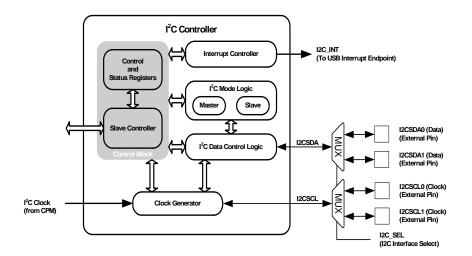

## **Chapter 12 I2C Controller**

| 12.1 | I2C Cont | troller Overview                                                     | 249 |

|------|----------|----------------------------------------------------------------------|-----|

| 12.2 | I2C Sub- | Modules                                                              | 250 |

|      | 12.2.1   | Control Block                                                        | 250 |

|      | 12.2.2   | Interrupt Controller                                                 | 250 |

|      | 12.2.3   | I2C Mode Logic                                                       | 251 |

|      | 12.2.4   | I2C Data Control Logic                                               | 251 |

|      | 12.2.5   | Clock Generator                                                      | 251 |

| 12.3 | I2C Tern | ninology                                                             | 251 |

|      | 12.3.1   | I2C Bus Terms.                                                       |     |

|      | 12.3.2   | I2C Bus Transfer Terms                                               | 252 |

| 12.4 | I2C Ope  | ration                                                               | 252 |

|      | 12.4.1   | Slave Mode Operation                                                 | 252 |

|      | 12.4.2   | Master Mode Operation                                                | 254 |

|      | 12.4.3   | Prioritizing Slave-Transmit Operation Over Master-Receiver Operation | 255 |

|      | 12.4.4  | Disabling the I2C Controller.                          |     |

|------|---------|--------------------------------------------------------|-----|

|      | 12.4.5  | I2CSCL Frequency Configuration                         |     |

|      | 12.4.6  |                                                        |     |

| 12.5 | -       |                                                        |     |

|      | 12.5.1  | Control Register (I2C_CONTROL)                         |     |

|      | 12.5.2  | Target Address Register (I2C_TAR)                      |     |

|      | 12.5.3  | Slave Address Register (I2C_SAR).                      |     |

|      | 12.5.4  | Rx/Tx Data Buffer and Command Register (I2C_DATA_CMD)  |     |

|      | 12.5.5  | SCL Clock High Count Register (I2C_SCL_HCNT)           |     |

|      | 12.5.6  | SCL Clock Low Count Register (I2C_SCL_LCNT)            |     |

|      | 12.5.7  | Masked Interrupt Status Register (I2C_MIS).            |     |

|      | 12.5.8  | Interrupt Mask Register (I2C_INTR_MASK)                |     |

|      | 12.5.9  | Raw Interrupt Status Register (I2C_RIS).               |     |

|      | 12.5.10 | Receive FIFO Threshold Register (I2C_RX_TL).           |     |

|      | 12.5.11 | Transmit FIFO Threshold Register (I2C_TX_TL)           |     |

|      | 12.5.12 |                                                        |     |

|      | 12.5.13 |                                                        |     |

|      | 12.5.14 |                                                        |     |

|      | 12.5.15 |                                                        |     |

|      | 12.5.16 |                                                        |     |

|      | 12.5.17 |                                                        |     |

|      | 12.5.18 | Clear RX_DONE Interrupt Register (I2C_CLR_RX_DONE)     |     |

|      | 12.5.19 | Clear ACTIVITY Interrupt Register (I2C_CLR_ACTIVITY)   |     |

|      | 12.5.20 | Clear STOP_DET Interrupt Register (I2C_CLR_STOP_DET)   | 281 |

|      | 12.5.21 | Clear START_DET Interrupt Register (I2C_CLR_START_DET) |     |

|      | 12.5.22 | Clear GEN_CALL Interrupt Register (I2C_CLR_GEN_CALL).  | 283 |

|      | 12.5.23 | I2C Enable Register (I2C_ENABLE)                       | 284 |

|      | 12.5.24 | Status Register (I2C_STATUS)                           |     |

|      | 12.5.25 | Transmit FIFO Level Register (I2C_TXFLR)               | 287 |

|      | 12.5.26 |                                                        | 288 |

|      | 12.5.27 | Transmit Abort Source Register (I2C_TX_ABRT_SRC)       | 289 |

|      | 12.5.28 | SDA Setup Register (I2C_SDA_SETUP)                     | 291 |

|      | 12.5.29 | ACK General Call Register (I2C_ACK_GEN_CALL).          | 292 |

|      | 12.5.30 | Enable Status Register (I2C_ENABLE_STATUS).            | 293 |

|      | 12.5.31 |                                                        |     |

|      | 12.5.32 | I2C Pin Control Register (I2C_PIN).                    | 296 |

|      | 12.5.33 | Sequential Data 0 Register (I2C_SEQ_DATA_0)            | 297 |

|      | 12.5.34 | Sequential Data 1 Register (I2C_SEQ_DATA_1)            | 298 |

|      | 12.5.35 | Sequential Data 2 Register (I2C_SEQ_DATA_2)            | 299 |

|      | 12.5.36 | Sequential Data 3 Register (I2C_SEQ_DATA_3)            | 300 |

|      | 12.5.37 | Sequential Data 4 Register (I2C_SEQ_DATA_4)            | 301 |

|      | 12.5.38 | Sequential Data 5 Register (I2C_SEQ_DATA_5)            | 302 |

|      | 12.5.39 | Sequential Data 6 Register (I2C_SEQ_DATA_6)            | 303 |

|      | 12.5.40 | Sequential Data 7 Register (I2C_SEQ_DATA_7)            | 304 |

|      | 12.5.41 | Sequential Data 8 Register (I2C_SEQ_DATA_8)            | 305 |

|      | 12.5.42 | Sequential Data 9 Register (I2C_SEQ_DATA_9)            | 306 |

|      | 12.5.43 | Sequential Data 10 Register (I2C_SEQ_DATA_10)          |     |

|      | 12.5.44 | Sequential Data 11 Register (I2C_SEQ_DATA_11)          |     |

|      | 12.5.45 | Sequential Data 12 Register (I2C_SEQ_DATA_12)          |     |

|      | 12.5.46 | Sequential Data 13 Register (I2C_SEQ_DATA_13)          |     |

|      | 12.5.47 | Sequential Data 14 Register (I2C_SEQ_DATA_14)          |     |

|      | 12.5.48 | Sequential Data 15 Register (I2C_SEQ_DATA_15)          | 312 |

# Chapter 13 System Control

| 13.1 | Overview | 13 |

|------|----------|----|

|      |          |    |

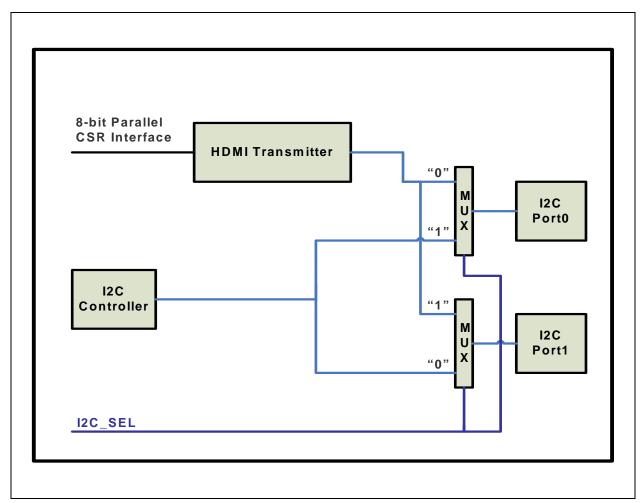

| 13.2 | I2C Selection |                                                     |       |

|------|---------------|-----------------------------------------------------|-------|

| 13.3 | Control a     | and Status Registers                                | . 314 |

|      | 13.3.1        | Device ID (ID_REV).                                 | . 315 |

|      | 13.3.2        | FPGA (FPGA_REV)                                     | . 316 |

|      | 13.3.3        | Hardware Configuration Register (HW_CFG)            | . 317 |

|      | 13.3.4        | I2C Interface Selection Register (I2C_SEL)          | . 319 |

| Chap | oter 14 N     | Aiscellaneous                                       |       |

| 14.1 | Overview      | Ν                                                   | . 320 |

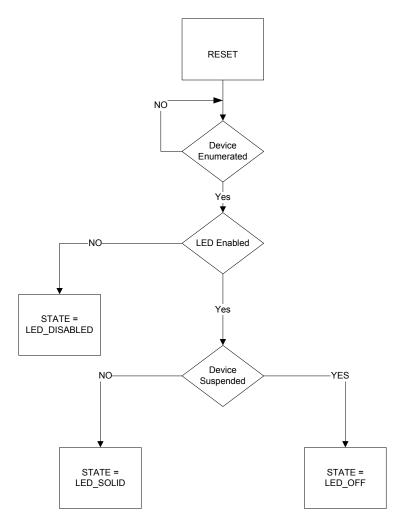

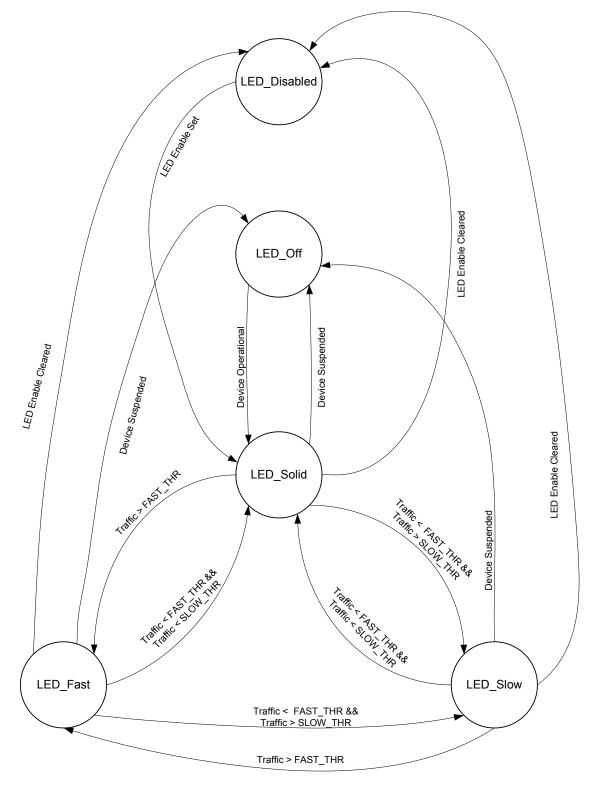

| 14.2 | LED Cor       | nfiguration                                         | . 320 |

| 14.3 | Audio Co      |                                                     | . 324 |

|      | 14.3.1        | I2S Audio                                           | . 324 |

|      | 14.3.2        | SDPIF Audio                                         | . 324 |

| 14.4 | Control a     | and Status Registers                                | . 325 |

|      | 14.4.1        | Data Port Select Register (DP_SEL)                  | . 326 |

|      | 14.4.2        | Data Port Command Register (DP_CMD)                 | . 328 |

|      | 14.4.3        | Data Port Address Register (DP_ADDR)                | . 329 |

|      | 14.4.4        | Data Port Data 0 Register (DP_DATA0)                | . 330 |

|      | 14.4.5        | Data Port Data 1 Register (DP_DATA1)                | . 331 |

|      | 14.4.6        | FIFO Status Register (FIFO_STATUS)                  | . 332 |

|      | 14.4.7        | Video DAC Configuration Register (VDAC_CFG)         |       |

|      | 14.4.8        | RGB Configuration Register (RGB_CFG)                | . 334 |

|      | 14.4.9        | External Reset Configuration Register (EXT_RST_CFG) |       |

|      | 14.4.10       | Audio Configuration Register (AUDIO_CFG)            | . 336 |

|      | 14.4.11       | Audio Frequency 0 Register (AUDIO_FREQ0)            | . 337 |

|      | 14.4.12       | Audio Frequency 1 Register (AUDIO_FREQ1)            | . 338 |

|      | 14.4.13       | HDMI Configuration Register (HDMI_CFG).             | . 339 |

|      | 14.4.14       |                                                     |       |

|      | 14.4.15       | LED Configuration Register 1 (LED_CFG1)             | . 341 |

|      | 14.4.16       | LED Configuration Register 2 (LED_CFG2)             | . 342 |

|      | 14.4.17       | GPIO Enable Register (GPIO_ENABLE).                 | . 343 |

|      | 14.4.18       | GPIO Buffer Type Register (GPIO_BUF)                | . 344 |

|      | 14.4.19       | GPIO Direction Register (GPIO_DIR)                  | . 345 |

|      | 14.4.20       | GPIO Data Register (GPIO_DATA).                     |       |

|      | 14.4.21       | BOS Attributes Register (BOS_ATTR)                  | . 347 |

|      | 14.4.22       |                                                     |       |

|      | 14.4.23       | FS Attributes Register (FS_ATTR)                    | . 349 |

|      | 14.4.24       | String Attributes Register 0 (STRNG_ATTR0)          | . 350 |

|      | 14.4.25       | String Attributes Register 1 (STRNG_ATTR1)          | . 351 |

## **Chapter 15 Operational Characteristics**

| Operatin | g Conditions**                                                                                                               | 352                                                                                         |

|----------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Package  | Thermal Specifications                                                                                                       | 353                                                                                         |

| Current  | Consumption                                                                                                                  | 353                                                                                         |

| 15.4.1   | SUSPEND Power State                                                                                                          | 353                                                                                         |

| 15.4.2   | Operational                                                                                                                  | 354                                                                                         |

|          |                                                                                                                              |                                                                                             |

| AC Spec  | sifications                                                                                                                  | 356                                                                                         |

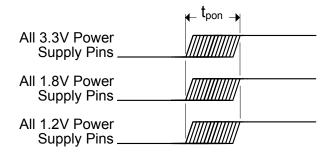

| 15.6.1   | Power Sequence Timing                                                                                                        | 357                                                                                         |

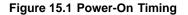

| 15.6.2   | Power-On Reset Timing                                                                                                        | 358                                                                                         |

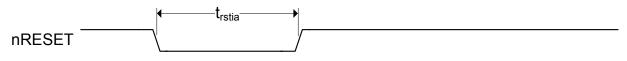

| 15.6.3   | Reset Timing                                                                                                                 |                                                                                             |

| 15.6.4   | Video DAC Timing                                                                                                             | 359                                                                                         |

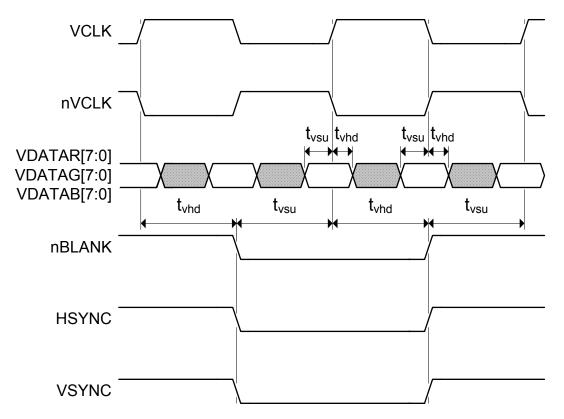

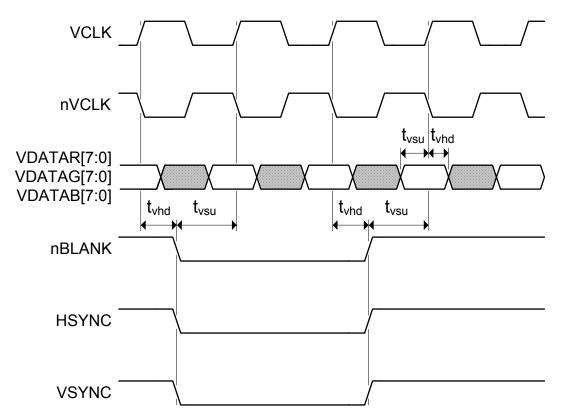

| 15.6.5   | Digital RGB Timing                                                                                                           | 360                                                                                         |

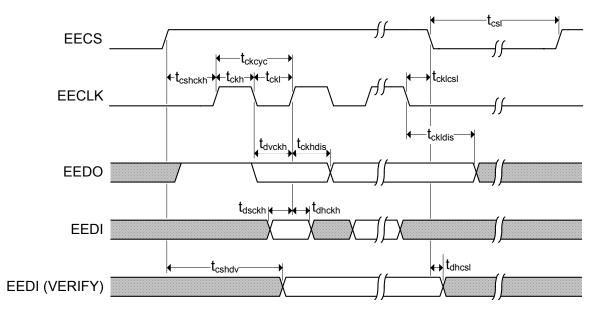

| 15.6.6   | EEPROM Timing                                                                                                                | 362                                                                                         |

|          | Operatin<br>Package<br>Current (<br>15.4.1<br>15.4.2<br>DC Spec<br>AC Spec<br>15.6.1<br>15.6.2<br>15.6.3<br>15.6.4<br>15.6.5 | 15.6.2Power-On Reset Timing15.6.3Reset Timing15.6.4Video DAC Timing15.6.5Digital RGB Timing |

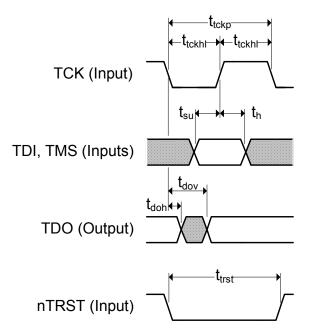

| 15.7 | 15.6.7 JTAG Timing |  |

|------|--------------------|--|

|      |                    |  |

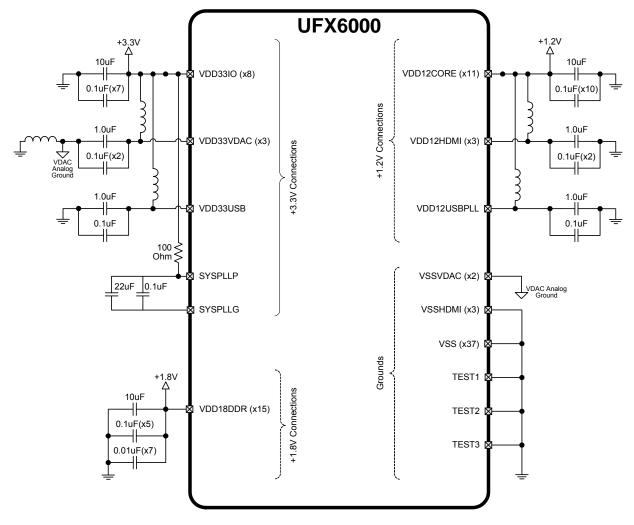

## **Chapter 17 Power Connections**

Chapter 18 Databook Revision History

# **List Of Tables**

| Table 1.1  | Register Bit Types                                          |   | 16 |

|------------|-------------------------------------------------------------|---|----|

| Table 2.1  | Graphics Engine Commands.                                   |   | 18 |

| Table 2.2  | Graphics Engine Compression Algorithms                      |   | 19 |

| Table 2.3  | UFX6000 Memory Map                                          |   |    |

|            | USB Pins                                                    |   |    |

|            | Digital RGB Pins                                            |   |    |

|            | RGB / DDR Mode Mapping Table                                |   |    |

|            | VDAC Pins.                                                  |   |    |

|            | DDR2 Memory Pins.                                           |   |    |

|            | HDMI Pins                                                   |   |    |

|            | EEPROM Pins                                                 |   |    |

|            | JTAG Pins                                                   |   |    |

|            | Miscellaneous Pins                                          |   |    |

|            | I/O Power Pins, Core Power Pins, and Ground Pins.           |   |    |

|            |                                                             |   |    |

|            | No-Connect Pins                                             |   |    |

|            | UFX6000 Bond Options                                        |   |    |

|            | 225-LFBGA Package Pin Assignments                           |   |    |

|            | Buffer Types                                                |   |    |

|            | Format of Register Write Setup Stage                        |   |    |

|            | Format of Register Write Data Stage.                        |   |    |

|            | Format of Register Read Setup Stage.                        |   |    |

|            | Format of Register Read Data Stage                          |   |    |

| Table 4.5  | Format of Register Read Setup Stage.                        | ' | 45 |

| Table 4.6  | Format of Get Statistics Setup Stage                        | ' | 46 |

| Table 4.7  | Format of Get Statistics Data Stage                         | ' | 46 |

| Table 4.8  | Interrupt Packet Format.                                    | ' | 47 |

| Table 4.9  | Device Descriptor                                           |   | 48 |

|            | Configuration Descriptor                                    |   |    |

|            | Interface Descriptor 0                                      |   |    |

|            | Endpoint 1 Descriptor                                       |   |    |

|            | Endpoint 2 Descriptor                                       |   |    |

|            | Other Speed Configuration Descriptor.                       |   |    |

|            | Device Qualifier Descriptor                                 |   |    |

|            | Binary Device Object Store Descriptor                       |   |    |

|            | USB 2.0 Extension Descriptor                                |   |    |

|            | LANGID String Descriptor                                    |   |    |

|            | String Descriptor (Indices 1-5).                            |   |    |

|            | USB Control and Status Register Map                         |   |    |

|            |                                                             |   |    |

|            | Power States                                                |   |    |

| Table 5.2  | Functionality to Power State Mapping - UFX6000              |   |    |

| Table 5.3  | Clocks                                                      |   |    |

|            | PLL Frequency Configurations                                |   |    |

|            | LPM States                                                  |   |    |

|            | LFPS States.                                                |   |    |

| Table 5.7  | Clocks and Power Management Control and Status Register Map |   |    |

| Table 6.1  | Chip Level Resets                                           |   | 85 |

| Table 7.1  | Sample Programming Values for DDR2                          |   |    |

| Table 7.2  | Memory Controller Control and Status Register Map           |   |    |

| Table 8.1  | EEPROM Format                                               |   |    |

| Table 8.2  | Configuration Flags 0                                       | 1 | 45 |

|            | EEPROM Defaults                                             |   |    |

|            | USB Control and Status Register Map                         |   |    |

| Table 10.1 | Display Cursor Status/Control Register Pairs                | 1 | 63 |

| Table 10.2 Display Controller Control and Status Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 171 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Table 10.3 Cursor Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 191 |

| Table 11.1 Graphics Engine Control and Status Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 235 |

| Table 12.1 Clearing Method of I2C Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 257 |

| Table 12.2 I2C Register Map.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 257 |

| Table 13.1 System Control Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 314 |

| Table 14.1 Miscellaneous Control and Status Register Map.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 325 |

| Table 14.2 Data Port Select Mapping Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 327 |

| Table 15.1 Package Thermal Parameters    Image: Comparison of the table of ta | . 353 |

| Table 15.2 SUSPEND Supply Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| Table 15.3 Typical High-Speed Operational Supply Current (mA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 354 |

| Table 15.4 I/O Buffer Characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 355 |

| Table 15.5 Video DAC - DC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 356 |

| Table 15.6 Power-On Timing Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 357 |

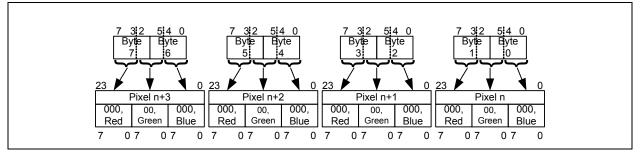

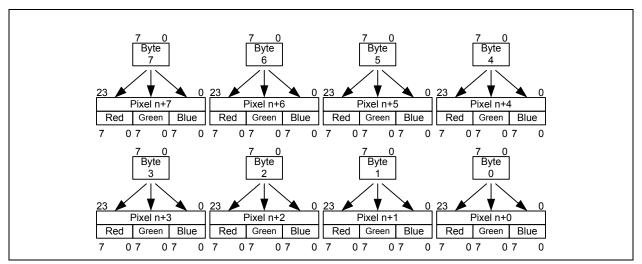

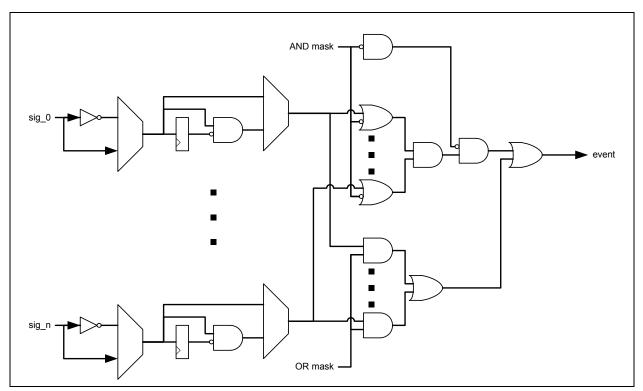

| Table 15.7 nRESET Power-On Timing Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 358 |