## LAN9512/LAN9512i

# USB 2.0 Hub and 10/100 Ethernet Controller

## PRODUCT FEATURES

#### **Highlights**

- Two downstream ports, one upstream port

- Two integrated downstream USB 2.0 PHYs

- One integrated upstream USB 2.0 PHY

- Integrated 10/100 Ethernet MAC with full-duplex support

- Integrated 10/100 Ethernet PHY with HP Auto-MDIX

- Implements Reduced Power Operating Modes

- Minimized BOM Cost

- Single 25 MHz crystal (Eliminates cost of separate crystals for USB and Ethernet)

- Built-in Power-On-Reset (POR) circuit (Eliminates requirement for external passive or active reset)

#### **Target Applications**

- Desktop PCs

- Notebook PCs

- Printers

- Game Consoles

- Embedded Systems

- Docking Stations

#### **Key Features**

- USB Hub

- Fully compliant with Universal Serial Bus Specification Revision 2.0

- HS (480 Mbps), FS (12 Mbps), and LS (1.5 Mbps) compatible

- Two downstream ports, one upstream port

- Port mapping and disable support

- Port Swap: Programmable USB diff-pair pin location

- PHY Boost: Programmable USB signal drive strength

- Select presence of a permanently hardwired USB peripheral device on a port by port basis

- Advanced power saving features

- Downstream PHY goes into low power mode when port power to the port is disabled

- Full Power Management with individual or ganged power control of each downstream port.

- Integrated USB termination Pull-up/Pull-down resistors

Internal short circuit protection of USB differential signal

- pins

- High-Performance 10/100 Ethernet Controller

- Fully compliant with IEEE802.3/802.3u

- Integrated Ethernet MAC and PHY

- 10BASE-T and 100BASE-TX support

- Full- and half-duplex support with flow control

- Preamble generation and removal

- Automatic 32-bit CRC generation and checking

- Automatic payload padding and pad removal

- Loop-back modes

- TCP/UDP checksum offload support

- Flexible address filtering modes

- One 48-bit perfect address

- 64 hash-filtered multicast addresses

- Pass all multicast

- Promiscuous mode

- Inverse filtering

- Pass all incoming with status report

- Wakeup packet support

- Integrated Ethernet PHY

- Auto-negotiation, HP Auto-MDIX

- Automatic polarity detection and correction

- Energy Detect

- Power and I/Os

- Three PHY LEDs

- Eight GPIOs

- Supports bus-powered and self-powered operation

- Internal 1.8v core supply regulator

- External 3.3v I/O supply

- Miscellaneous features

- Optional EEPROM

- Optional 24MHz reference clock output for partner hub

- IEEE 1149.1 (JTAG) Boundary Scan

- Software

- Windows 2000/XP/Vista Driver

- Linux Driver

- Win CE Driver

- MAC OS Driver

- EEPROM Utility

- Packaging

- 64-pin QFN, lead-free RoHS compliant

- Environmental

- Commercial Temperature Range (0°C to +70°C)

- Industrial Temperature Range (-40°C to +85°C)

- ±8kV HBM without External Protection Devices

- ±8kV contact mode (IEC61000-4-2)

- ±15kV air-gap discharge mode (IEC61000-4-2)

#### SMSC CONFIDENTIAL DATABOOK

#### **Order Numbers:**

LAN9512-JZX for 64-pin, QFN lead-free RoHS compliant package (0 to +70°C temp range) LAN9512i-JZX for 64-pin, QFN lead-free RoHS compliant package (-40 to +85°C temp range)

This product meets the halogen maximum concentration values per IEC61249-2-21 For RoHS compliance and environmental information, please visit www.smsc.com/rohs

Copyright © 2012 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as nomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

# **Table of Contents**

| Chap                            | ter 1 In                                                                                                                                                                                                                                  | troduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13                                                                                                                                                |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1                             | General T                                                                                                                                                                                                                                 | erms and Conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13                                                                                                                                                |

| 1.2                             |                                                                                                                                                                                                                                           | gram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                   |

|                                 |                                                                                                                                                                                                                                           | Dverview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                   |

|                                 |                                                                                                                                                                                                                                           | JSB Hub                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                   |

|                                 |                                                                                                                                                                                                                                           | Ethernet Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                   |

|                                 | 1.2.3.1                                                                                                                                                                                                                                   | USB Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                   |

|                                 | 1.2.3.2                                                                                                                                                                                                                                   | FIFO Controller (FCT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                   |

|                                 | 1.2.3.3                                                                                                                                                                                                                                   | Transaction Layer Interface (TLI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |

|                                 | 1.2.3.4                                                                                                                                                                                                                                   | Ethernet MAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                   |

|                                 | 1.2.3.5                                                                                                                                                                                                                                   | Control and Status Registers (CSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                   |

|                                 |                                                                                                                                                                                                                                           | Ethernet PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                   |

|                                 |                                                                                                                                                                                                                                           | EEPROM Controller (EPC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                   |

|                                 |                                                                                                                                                                                                                                           | Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                   |

|                                 | -                                                                                                                                                                                                                                         | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                   |

|                                 |                                                                                                                                                                                                                                           | Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                   |

|                                 | -                                                                                                                                                                                                                                         | rest Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                   |

|                                 | -                                                                                                                                                                                                                                         | System Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                   |

|                                 | 1.2.10                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10                                                                                                                                                |

| Chap                            | ter 2 Pi                                                                                                                                                                                                                                  | n Description and Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20                                                                                                                                                |

| 2.1                             |                                                                                                                                                                                                                                           | nnections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                   |

| 2.2                             | Port Powe                                                                                                                                                                                                                                 | er Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28                                                                                                                                                |

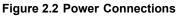

|                                 | 2.2.1 I                                                                                                                                                                                                                                   | Port Power Control Using a USB Power Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28                                                                                                                                                |

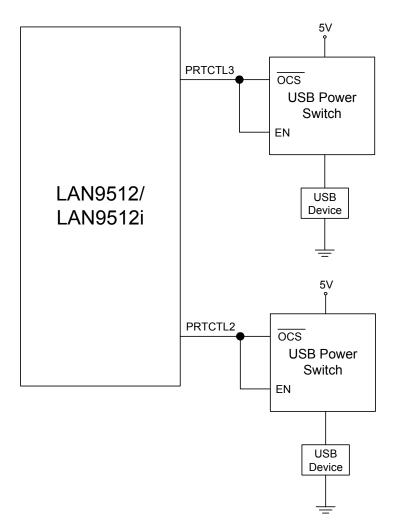

|                                 | 2.2.2                                                                                                                                                                                                                                     | Port Power Control Using a Poly Fuse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29                                                                                                                                                |

| 2.3                             | Buffer Typ                                                                                                                                                                                                                                | bes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31                                                                                                                                                |

|                                 |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                   |

| Chan                            | tor 3 Fi                                                                                                                                                                                                                                  | unctional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37                                                                                                                                                |

| Chap                            |                                                                                                                                                                                                                                           | Inctional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                   |

| 3.1                             | Functiona                                                                                                                                                                                                                                 | l Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32                                                                                                                                                |

| 3.1<br>3.2                      | Functiona<br>USB Com                                                                                                                                                                                                                      | l Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32<br>32                                                                                                                                          |

| 3.1<br>3.2<br>3.3               | Functiona<br>USB Com<br>Clock Ger                                                                                                                                                                                                         | I Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32<br>32<br>32                                                                                                                                    |

| 3.1<br>3.2<br>3.3<br>3.4        | Functiona<br>USB Com<br>Clock Ger<br>USB PHY                                                                                                                                                                                              | I Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32<br>32<br>32<br>32                                                                                                                              |

| 3.1<br>3.2<br>3.3               | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub.                                                                                                                                                                                  | I Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32<br>32<br>32<br>32<br>32                                                                                                                        |

| 3.1<br>3.2<br>3.3<br>3.4        | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub<br>3.5.1                                                                                                                                                                          | I Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32<br>32<br>32<br>32<br>32<br>32<br>33                                                                                                            |

| 3.1<br>3.2<br>3.3<br>3.4        | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub<br>3.5.1 I<br>3.5.2 I                                                                                                                                                             | I Overview .<br>mon Block (UCB) .<br>merator and Power Management Controller (CPM) .<br>s .<br>Hub Configuration Options .<br>Power Switching Polarity .                                                                                                                                                                                                                                                                                                                                                                     | 32<br>32<br>32<br>32<br>32<br>33<br>33                                                                                                            |

| 3.1<br>3.2<br>3.3<br>3.4        | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub<br>3.5.1 H<br>3.5.2 H<br>3.5.3 N                                                                                                                                                  | I Overview .<br>mon Block (UCB) .<br>herator and Power Management Controller (CPM) .<br>s<br>Hub Configuration Options .<br>Power Switching Polarity .                                                                                                                                                                                                                                                                                                                                                                       | 32<br>32<br>32<br>32<br>32<br>33<br>33<br>33                                                                                                      |

| 3.1<br>3.2<br>3.3<br>3.4        | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub<br>3.5.1 H<br>3.5.2 H<br>3.5.3 N<br>3.5.4 H                                                                                                                                       | I Overview .<br>mon Block (UCB)<br>herator and Power Management Controller (CPM)<br>s<br>Hub Configuration Options<br>Power Switching Polarity<br>/Bus Detect.<br>Hub USB Descriptors                                                                                                                                                                                                                                                                                                                                        | 32<br>32<br>32<br>32<br>32<br>33<br>33<br>33<br>33                                                                                                |

| 3.1<br>3.2<br>3.3<br>3.4        | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub<br>3.5.1 H<br>3.5.2 H<br>3.5.3 M<br>3.5.4 H<br>3.5.4 H                                                                                                                            | I Overview .<br>mon Block (UCB)<br>herator and Power Management Controller (CPM) .<br>                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32<br>32<br>32<br>32<br>33<br>33<br>33<br>33<br>.34                                                                                               |

| 3.1<br>3.2<br>3.3<br>3.4        | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub<br>3.5.1 H<br>3.5.2 H<br>3.5.3 N<br>3.5.4 H<br>3.5.4.1<br>3.5.4.2                                                                                                                 | I Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32<br>32<br>32<br>32<br>33<br>33<br>33<br>33<br>.34<br>.37                                                                                        |

| 3.1<br>3.2<br>3.3<br>3.4        | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub<br>3.5.1 H<br>3.5.2 H<br>3.5.3 N<br>3.5.4 H<br>3.5.4.1<br>3.5.4.2<br>3.5.4.3                                                                                                      | I Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32<br>32<br>32<br>32<br>33<br>33<br>33<br>33<br>.34<br>.37<br>)45                                                                                 |

| 3.1<br>3.2<br>3.3<br>3.4        | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub<br>3.5.1 H<br>3.5.2 H<br>3.5.3 N<br>3.5.4 H<br>3.5.4.1<br>3.5.4.2<br>3.5.4.3<br>3.5.4.3<br>3.5.4.4                                                                                | I Overview .<br>mon Block (UCB)<br>herator and Power Management Controller (CPM)<br>s<br>Hub Configuration Options<br>Power Switching Polarity<br>/Bus Detect.<br>Hub USB Descriptors<br>Hub Attached as a Full-Speed Device, (High-Speed Disabled).<br>Hub Attached as a Full-Speed Device, But is High-Speed Capable.<br>Hub Attached as a High-Speed Device (OEM-Configured for Single-TT Support Only<br>Hub Attached as a High-Speed Device (OEM-Configured as Multi-TT Capable)                                        | 32<br>32<br>32<br>32<br>33<br>33<br>33<br>.34<br>.37<br>)45<br>.51                                                                                |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub<br>3.5.1 H<br>3.5.2 H<br>3.5.3 N<br>3.5.4 H<br>3.5.4.1<br>3.5.4.2<br>3.5.4.3<br>3.5.4.3<br>3.5.4.4<br>3.5.4.5                                                                     | I Overview .<br>mon Block (UCB)<br>herator and Power Management Controller (CPM)<br>s<br>Hub Configuration Options<br>Power Switching Polarity<br>/Bus Detect.<br>Hub USB Descriptors<br>Hub Attached as a Full-Speed Device, (High-Speed Disabled).<br>Hub Attached as a Full-Speed Device, But is High-Speed Capable.<br>Hub Attached as a High-Speed Device (OEM-Configured for Single-TT Support Only<br>Hub Attached as a High-Speed Device (OEM-Configured as Multi-TT Capable)<br>Class-Specific Hub Descriptor       | 32<br>32<br>32<br>32<br>33<br>33<br>33<br>33<br>.34<br>.51<br>.58                                                                                 |

| 3.1<br>3.2<br>3.3<br>3.4        | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub<br>3.5.1 H<br>3.5.2 H<br>3.5.3 N<br>3.5.4 H<br>3.5.4.1<br>3.5.4.2<br>3.5.4.3<br>3.5.4.3<br>3.5.4.4<br>3.5.4.5<br>USB 2.0 E                                                        | I Overview .<br>mon Block (UCB)<br>herator and Power Management Controller (CPM) .<br>s<br>Hub Configuration Options .<br>Power Switching Polarity .<br>/Bus Detect.<br>Hub USB Descriptors<br>Hub Attached as a Full-Speed Device, (High-Speed Disabled).<br>Hub Attached as a Full-Speed Device, But is High-Speed Capable.<br>Hub Attached as a High-Speed Device (OEM-Configured for Single-TT Support Only<br>Hub Attached as a High-Speed Device (OEM-Configured as Multi-TT Capable)<br>Class-Specific Hub Descriptor | 32<br>32<br>32<br>32<br>33<br>33<br>33<br>33<br>.34<br>.37<br>.51<br>.58<br>60                                                                    |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub<br>3.5.1 H<br>3.5.2 H<br>3.5.3 N<br>3.5.4 H<br>3.5.4.1<br>3.5.4.2<br>3.5.4.3<br>3.5.4.3<br>3.5.4.4<br>3.5.4.5<br>USB 2.0 H<br>3.6.1 S                                             | I Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32<br>32<br>32<br>32<br>33<br>33<br>33<br>33<br>33<br>.34<br>.51<br>.58<br>60<br>60                                                               |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub<br>3.5.1 H<br>3.5.2 H<br>3.5.3 N<br>3.5.4 H<br>3.5.4.1<br>3.5.4.2<br>3.5.4.3<br>3.5.4.3<br>3.5.4.4<br>3.5.4.5<br>USB 2.0 H<br>3.6.1 S<br>3.6.1.1                                  | I Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32<br>32<br>32<br>32<br>33<br>33<br>33<br>33<br>.34<br>.51<br>.58<br>60<br>60<br>.60                                                              |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub<br>3.5.1 H<br>3.5.2 H<br>3.5.3 N<br>3.5.4 H<br>3.5.4.1<br>3.5.4.2<br>3.5.4.3<br>3.5.4.3<br>3.5.4.4<br>3.5.4.5<br>USB 2.0 E<br>3.6.1 1<br>3.6.1.2                                  | I Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32<br>32<br>32<br>32<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>3                                                                   |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub<br>3.5.1 H<br>3.5.2 H<br>3.5.3 N<br>3.5.4 H<br>3.5.4.1<br>3.5.4.2<br>3.5.4.3<br>3.5.4.3<br>3.5.4.4<br>3.5.4.5<br>USB 2.0 H<br>3.6.1.1<br>3.6.1.2<br>3.6.1.3                       | I Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32<br>32<br>32<br>33<br>33<br>33<br>33<br>33<br>.34<br>.51<br>.58<br>60<br>.60<br>.60<br>.63<br>.64                                               |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub<br>3.5.1 H<br>3.5.2 H<br>3.5.2 H<br>3.5.3 N<br>3.5.4 H<br>3.5.4.1<br>3.5.4.2<br>3.5.4.3<br>3.5.4.4<br>3.5.4.5<br>USB 2.0 H<br>3.6.1 S<br>3.6.1.1<br>3.6.1.2<br>3.6.1.3<br>3.6.1.4 | I Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\begin{array}{c} 32\\ 32\\ 32\\ 32\\ 33\\ 33\\ 33\\ 33\\ .34\\ .51\\ .58\\ 60\\ .60\\ .63\\ .64\\ .65\\ \end{array}$                             |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub<br>3.5.1 F<br>3.5.2 F<br>3.5.3 N<br>3.5.4 F<br>3.5.4.1<br>3.5.4.2<br>3.5.4.3<br>3.5.4.4<br>3.5.4.5<br>USB 2.0 F<br>3.6.1 S<br>3.6.1.1<br>3.6.1.2<br>3.6.1.3<br>3.6.1.4<br>3.6.2 F | I Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\begin{array}{c} 32\\ 32\\ 32\\ 32\\ 32\\ 33\\ 33\\ 33\\ 33\\ .34\\ .37\\ .51\\ .58\\ 60\\ .60\\ .60\\ .63\\ .64\\ .65\\ 65\\ \end{array}$       |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub<br>3.5.1 H<br>3.5.2 H<br>3.5.3 N<br>3.5.4 H<br>3.5.4.1<br>3.5.4.2<br>3.5.4.3<br>3.5.4.4<br>3.5.4.5<br>USB 2.0 H<br>3.6.1.1<br>3.6.1.2<br>3.6.1.3<br>3.6.1.4<br>3.6.2 H<br>3.6.3 H | I Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\begin{array}{c} 32\\ 32\\ 32\\ 32\\ 33\\ 33\\ 33\\ 33\\ .34\\ .51\\ .58\\ 60\\ .60\\ .60\\ .63\\ .64\\ .65\\ 65\\ 67\\ \end{array}$             |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Functiona<br>USB Com<br>Clock Ger<br>USB PHY<br>USB Hub<br>3.5.1 F<br>3.5.2 F<br>3.5.3 N<br>3.5.4 F<br>3.5.4.1<br>3.5.4.2<br>3.5.4.3<br>3.5.4.4<br>3.5.4.5<br>USB 2.0 F<br>3.6.1 S<br>3.6.1.1<br>3.6.1.2<br>3.6.1.3<br>3.6.1.4<br>3.6.2 F | I Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\begin{array}{c} 32\\ 32\\ 32\\ 32\\ 33\\ 33\\ 33\\ 33\\ 33\\ .34\\ .51\\ .58\\ 60\\ .60\\ .60\\ .63\\ .64\\ .65\\ 67\\ .67\\ .67\\ \end{array}$ |

|     | 3.6.3.3  | Interface Descriptor 0 Default            | .69 |

|-----|----------|-------------------------------------------|-----|

|     | 3.6.3.4  | Endpoint 1 (Bulk In) Descriptor           | .69 |

|     | 3.6.3.5  | Endpoint 2 (Bulk Out) Descriptor          | .70 |

|     | 3.6.3.6  | Endpoint 3 (Interrupt) Descriptor         | .70 |

|     | 3.6.3.7  | Other Speed Configuration Descriptor      | .71 |

|     | 3.6.3.8  | Device Qualifier Descriptor               | .72 |

|     | 3.6.3.9  | String Descriptors                        | .73 |

|     | 3.6.4    | Statistics                                | 74  |

|     | 3.6.5    | USB Standard Commands                     | 75  |

|     | 3.6.5.1  | Clear Feature                             | .75 |

|     | 3.6.5.2  | Get Configuration                         | .75 |

|     | 3.6.5.3  | Get Descriptor                            | .76 |

|     | 3.6.5.4  | Get Interface                             |     |

|     | 3.6.5.5  | Get Status                                | .77 |

|     | 3.6.6    | USB Vendor Commands                       | 81  |

|     | 3.6.6.1  | Register Write Command                    |     |

|     | 3.6.6.2  | Register Read Command                     |     |

|     | 3.6.6.3  | Get Statistics Command                    | .82 |

| 3.7 | FIFO Co  | ntroller (FCT)                            |     |

|     | 3.7.1    | RX Path (Ethernet -> USB)                 |     |

|     | 3.7.1.1  | RX Error Detection                        | .85 |

|     | 3.7.1.2  | RX Status Format                          | .86 |

|     | 3.7.1.3  | Flushing the RX FIFO                      | .87 |

|     | 3.7.1.4  | Stopping and Starting the Receiver        | .87 |

|     | 3.7.2    | TX Path (USB -> Ethernet)                 | 87  |

|     | 3.7.2.1  | TX Command Format                         | .89 |

|     | 3.7.2.2  | TX Data Format                            | .90 |

|     | 3.7.2.3  | TX Buffer Fragmentation Rules             | .90 |

|     | 3.7.2.4  | FCT Actions                               | .91 |

|     | 3.7.2.5  | TX Error Detection                        | .91 |

|     | 3.7.2.6  | TX Status Format                          |     |

|     | 3.7.2.7  | Transmit Examples                         |     |

|     | 3.7.2.8  | TX Example 2                              |     |

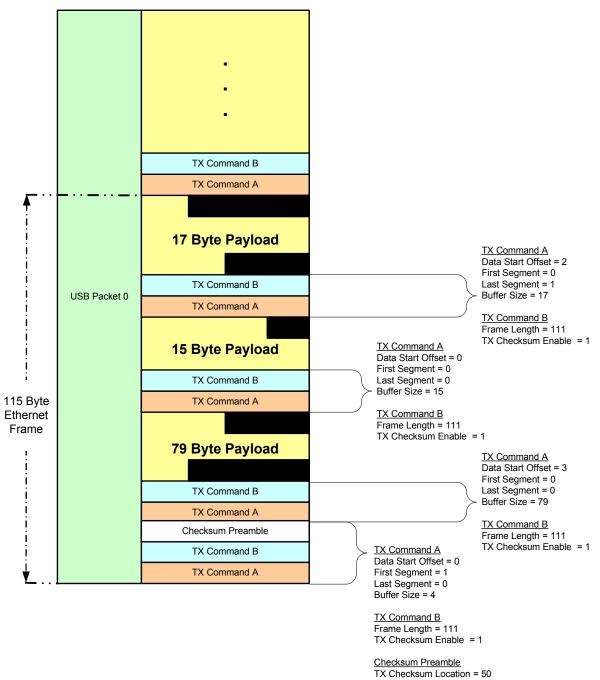

|     | 3.7.2.9  | TX Example 3                              |     |

|     | 3.7.2.10 |                                           |     |

|     | 3.7.2.11 |                                           |     |

|     |          | Arbitration                               |     |

| 3.8 |          | thernet MAC                               |     |

|     | 3.8.1    | Flow Control                              |     |

|     | 3.8.1.1  | Full-Duplex Flow Control                  |     |

|     | 3.8.1.2  | Half-Duplex Flow Control (Backpressure)   |     |

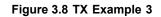

|     | 3.8.2    | Virtual Local Area Network (VLAN) Support |     |

|     | 3.8.3    | Address Filtering Functional Description  |     |

|     | 3.8.4    | Filtering Modes                           |     |

|     | 3.8.4.1  | Perfect Filtering                         |     |

|     | 3.8.4.2  | Hash Only Filtering Mode                  |     |

|     | 3.8.4.3  | Hash Perfect Filtering                    |     |

|     | 3.8.4.4  | Inverse Filtering                         |     |

|     | 3.8.5    | Wakeup Frame Detection                    |     |

|     | 3.8.5.1  | Magic Packet Detection                    |     |

|     | 3.8.6    | Receive Checksum Offload Engine (RXCOE).  |     |

|     | 3.8.6.1  | RX Checksum Calculation                   |     |

|     | 3.8.7    | Transmit Checksum Offload Engine (TXCOE)  |     |

|     | 3.8.7.1  | TX Checksum Calculation                   | 112 |

|      | 3.8.8 MAC Control and Status Registers (MCSR)                                | 112 |

|------|------------------------------------------------------------------------------|-----|

| 3.9  | 10/100 Ethernet PHY                                                          | 112 |

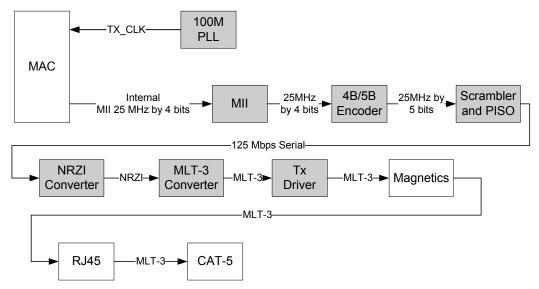

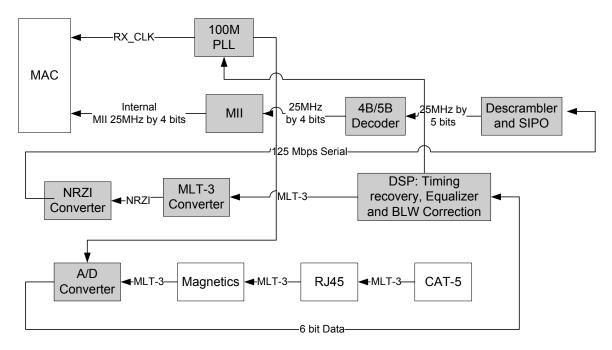

|      | 3.9.1 100BASE-TX Transmit                                                    | 112 |

|      | 3.9.1.1 4B/5B Encoding                                                       | 113 |

|      | 3.9.1.2 Scrambling                                                           | 114 |

|      | 3.9.1.3 NRZI and MLT3 Encoding                                               | 115 |

|      | 3.9.1.4 100M Transmit Driver                                                 |     |

|      | 3.9.1.5 100M Phase Lock Loop (PLL)                                           | 115 |

|      | 3.9.2 100BASE-TX Receive                                                     |     |

|      | 3.9.2.1 100M Receive Input                                                   |     |

|      | 3.9.2.2 Equalizer, Baseline Wander Correction and Clock and Data Recovery    |     |

|      | 3.9.2.3 NRZI and MLT-3 Decoding                                              |     |

|      | 3.9.2.4 Descrambling                                                         |     |

|      | 3.9.2.5 Alignment                                                            |     |

|      | 3.9.2.6 5B/4B Decoding                                                       |     |

|      | 3.9.2.7 Receiver Errors                                                      |     |

|      | 3.9.3 10BASE-T Transmit                                                      |     |

|      | 3.9.3.1 10M Transmit Data Across the Internal MII Bus                        |     |

|      | 3.9.3.2 Manchester Encoding                                                  |     |

|      | 3.9.3.3 10M Transmit Drivers                                                 |     |

|      |                                                                              |     |

|      | 3.9.4 10BASE-T Receive                                                       |     |

|      | 3.9.4.1 10M Receive Input and Squelch                                        |     |

|      | 3.9.4.2 Manchester Decoding                                                  |     |

|      | 3.9.4.3 Jabber Detection                                                     |     |

|      | 3.9.5 Auto-negotiation                                                       |     |

|      | 3.9.6 Parallel Detection                                                     |     |

|      | 3.9.6.1 Re-starting Auto-negotiation                                         |     |

|      | 3.9.6.2 Disabling Auto-negotiation                                           |     |

|      | 3.9.6.3 Half vs. Full-Duplex                                                 |     |

|      | 3.9.7 HP Auto-MDIX                                                           |     |

|      | 3.9.8 PHY Power-Down Modes                                                   |     |

|      | 3.9.8.1 General Power-Down                                                   |     |

|      | 3.9.8.2 Energy Detect Power-Down                                             |     |

|      | 3.9.9 PHY Resets                                                             |     |

|      | 3.9.9.1 PHY Soft Reset via PMT_CTL Register PHY Reset (PHY_RST) Bit          |     |

|      | 3.9.9.2 PHY Soft Reset via PHY Basic Control Register Bit 15 (PHY Reg. 0.15) | 122 |

|      | 3.9.10 Required Ethernet Magnetics                                           | 122 |

|      | 3.9.11 PHY Registers                                                         | 122 |

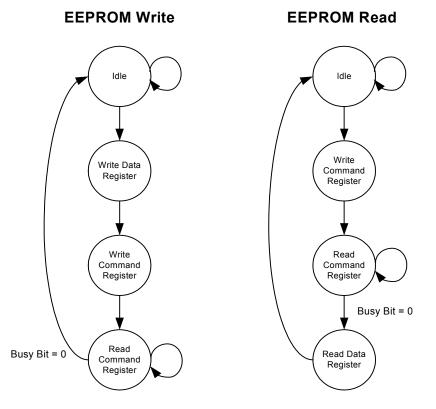

| 3.10 | EEPROM Controller (EPC).                                                     | 123 |

|      | 3.10.1 EEPROM Format                                                         | 123 |

|      | 3.10.2 EEPROM Defaults                                                       | 126 |

|      | 3.10.3 EEPROM Auto-Load                                                      | 127 |

|      | 3.10.4 EEPROM Host Operations                                                | 127 |

|      | 3.10.4.1 Supported EEPROM Operations                                         |     |

|      | 3.10.4.2 Host Initiated EEPROM Reload                                        |     |

|      | 3.10.4.3 EEPROM Command and Data Registers                                   |     |

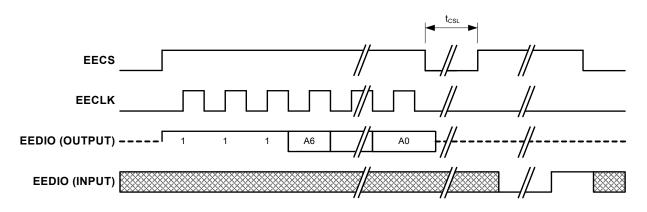

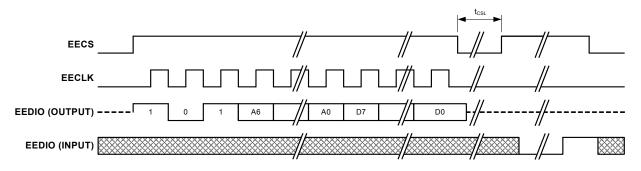

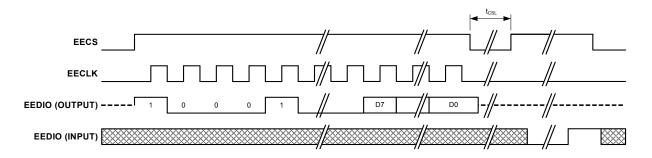

|      | 3.10.4.4 EEPROM Timing                                                       |     |

|      | 3.10.5 An Example of EEPROM Format Interpretation                            |     |

| 3.11 | Device Clocking                                                              |     |

| 3.12 | Device Power Sources                                                         |     |

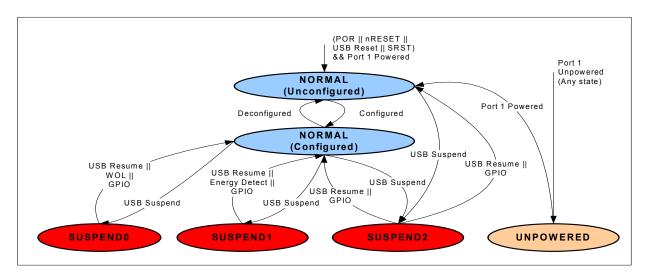

| 3.13 | Ethernet Controller Power States                                             |     |

| 5.10 | 3.13.1 UNPOWERED State                                                       |     |

|      | 3.13.2 NORMAL State                                                          |     |

|      | 3.13.2.1 Unconfigured                                                        |     |

|      | 3.13.2.2 | 2 Reset Operation                                                | .139  |

|------|----------|------------------------------------------------------------------|-------|

|      | 3.13.2.3 | 3 Suspend Operation                                              | .139  |

|      | 3.13.3   | SUSPEND States                                                   | 139   |

|      | 3.13.3.  | 1 Reset from Suspend                                             | . 140 |

|      | 3.13.3.2 | 2 SUSPEND0                                                       | .140  |

|      | 3.13.3.3 | 3 SUSPEND1                                                       | .140  |

|      | 3.13.3.4 | 4 SUSPEND2                                                       | .140  |

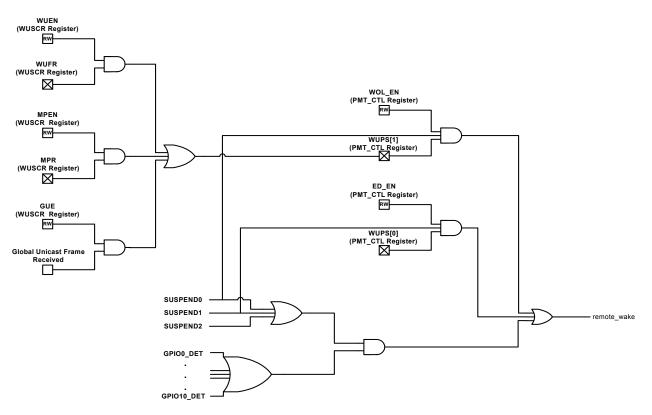

| 3.14 | Wake Ev  | /ents                                                            | 140   |

|      | 3.14.1   | Detecting Wakeup Events                                          | 141   |

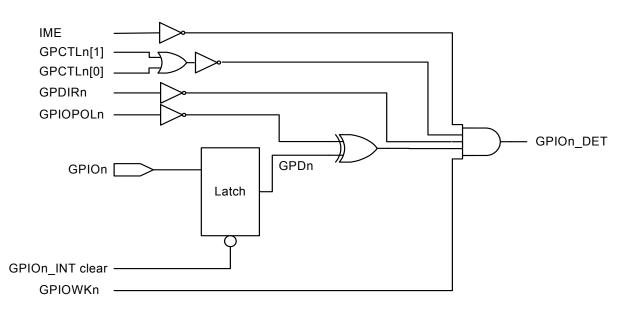

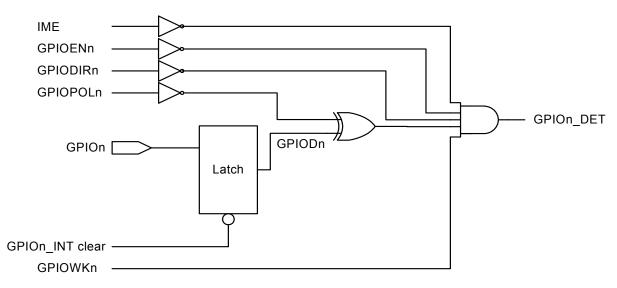

|      | 3.14.1.  | 1 Enabling GPIO Wake Events                                      | .143  |

|      | 3.14.1.  | 2 Enabling Wakeup Frame Wake Events                              | .144  |

|      | 3.14.2   | Enabling Link Status Change (Energy Detect) Wake Events          |       |

| 3.15 | Resets.  | · · · · · · · · · · · · · · · · · · ·                            |       |

|      | 3.15.1   | Power-On Reset (POR).                                            |       |

|      | 3.15.2   | External Chip Reset (nRESET)                                     |       |

|      | 3.15.3   | Lite Reset (LRST)                                                |       |

|      | 3.15.4   | Soft Reset (SRST)                                                |       |

|      | 3.15.5   | USB Reset.                                                       |       |

|      | 3.15.6   | PHY Software Reset                                               |       |

|      | 3.15.7   | nTRST                                                            |       |

|      | 3.15.8   | VBUS DET                                                         |       |

|      |          |                                                                  |       |

| Char | oter 4 F | Register Descriptions                                            | 148   |

| 4.1  | Register | Nomenclature                                                     | 148   |

| 4.2  | 0        | Memory Map                                                       |       |

| 4.3  | •        | Control and Status Registers.                                    |       |

|      | 4.3.1    | Device ID and Revision Register (ID_REV).                        |       |

|      | 4.3.2    | Interrupt Status Register (INT_STS)                              |       |

|      | 4.3.3    | Receive Configuration Register (RX CFG).                         |       |

|      | 4.3.4    | Transmit Configuration Register (TX_CFG)                         |       |

|      | 4.3.5    | Hardware Configuration Register (HW_CFG)                         |       |

|      | 4.3.6    | Receive FIFO Information Register (RX_FIFO_INF).                 |       |

|      | 4.3.7    | Transmit FIFO Information Register (TX_FIFO_INF)                 |       |

|      | 4.3.8    | Power Management Control Register (PMT_CTL)                      |       |

|      | 4.3.9    | LED General Purpose IO Configuration Register (LED GPIO CFG)     |       |

|      | 4.3.10   | General Purpose IO Configuration Register (GPIO_CFG)             |       |

|      | 4.3.11   | Automatic Flow Control Configuration Register (AFC_CFG).         |       |

|      | 4.3.12   | EEPROM Command Register (E2P CMD).                               |       |

|      | 4.3.13   | EEPROM Data Register (E2P_DATA)                                  |       |

|      | 4.3.14   | Burst Cap Register (BURST_CAP)                                   |       |

|      | 4.3.15   | Data Port Select Register (DP_SEL).                              |       |

|      | 4.3.16   | Data Port Command Register (DP_CMD).                             |       |

|      | 4.3.17   | Data Port Address Register (DP_ADDR)                             |       |

|      | 4.3.18   | Data Port Data 0 Register (DP_DATA0)                             |       |

|      | 4.3.19   | Data Port Data 1 Register (DP_DATA1)                             |       |

|      | 4.3.20   | General Purpose IO Wake Enable and Polarity Register (GPIO_WAKE) |       |

|      | 4.3.21   | Interrupt Endpoint Control Register (INT_EP_CTL)                 |       |

|      | 4.3.22   | Bulk In Delay Register (BULK_IN_DLY)                             |       |

| 4.4  |          | ntrol and Status Registers.                                      |       |

| 1. T | 4.4.1    | MAC Control Register (MAC_CR)                                    |       |

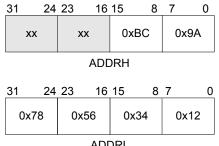

|      | 4.4.2    | MAC Address High Register (ADDRH)                                |       |

|      | 4.4.3    | MAC Address Low Register (ADDRL).                                |       |

|      | 4.4.4    | Multicast Hash Table High Register (HASHH)                       |       |

|      | 4.4.5    | Multicast Hash Table Low Register (HASHL)                        |       |

|      | 1.4.0    |                                                                  | 107   |

6 SMSC CONFIDENTIAL DATABOOK

|      | 4.4.6          | MII Access Register (MII_ACCESS)                                       | 188 |

|------|----------------|------------------------------------------------------------------------|-----|

|      | 4.4.7          | MII Data Register (MII_DATA).                                          |     |

|      | 4.4.8          | Flow Control Register (FLOW)                                           | 190 |

|      | 4.4.9          | VLAN1 Tag Register (VLAN1)                                             |     |

|      | 4.4.10         | VLAN2 Tag Register (VLAN2)                                             |     |

|      | 4.4.11         | Wakeup Frame Filter (WUFF)                                             |     |

|      | 4.4.12         | Wakeup Control and Status Register (WUCSR)                             |     |

|      | 4.4.13         | Checksum Offload Engine Control Register (COE_CR)                      |     |

| 4.5  |                | gisters                                                                |     |

|      | 4.5.1          | Basic Control Register                                                 |     |

|      | 4.5.2          | Basic Status Register                                                  |     |

|      | 4.5.3          | PHY Identifier 1 Register                                              |     |

|      | 4.5.4          | PHY Identifier 2 Register                                              |     |

|      | 4.5.5          | Auto Negotiation Advertisement Register                                |     |

|      | 4.5.6          | Auto Negotiation Link Partner Ability Register.                        |     |

|      | 4.5.7          | Auto Negotiation Expansion Register                                    |     |

|      | 4.5.8          | Mode Control/Status Register                                           |     |

|      | 4.5.9          | Special Modes Register.                                                |     |

|      | 4.5.10         | Special Control/Status Indications Register.                           |     |

|      | 4.5.11         | Interrupt Source Flag Register                                         |     |

|      | 4.5.12         | Interrupt Mask Register                                                |     |

| 16   | 4.5.13         | PHY Special Control/Status Register                                    |     |

| 4.6  |                | Infiguration Registers (HCFG)                                          |     |

|      | 4.6.1<br>4.6.2 | Vendor ID LSB (VIDL) Register                                          |     |

|      | 4.6.2<br>4.6.3 | Vendor ID MSB (VIDM) Register                                          |     |

|      | 4.6.3<br>4.6.4 | Product ID LSB (PIDL) Register                                         |     |

|      | 4.6.5          | Product ID MSB (PIDM) Register                                         |     |

|      | 4.6.5<br>4.6.6 | Device ID LSB (DIDL) Register                                          |     |

|      | 4.6.7          | Config Data Byte 1 (CFG1) Register                                     |     |

|      | 4.6.8          | Config Data Byte 2 (CFG2) Register                                     |     |

|      | 4.6.9          | Config Data Byte 3 (CFG3) Register                                     |     |

|      | 4.6.10         | Non-Removable Devices (NRD) Register                                   |     |

|      | 4.6.11         | Port Disable For Self-Powered Operation (PDS) Register                 |     |

|      | 4.6.12         | Port Disable For Bus-Powered Operation (PDB) Register                  |     |

|      | 4.6.13         | Max Power For Self-Powered Operation (MAXPS) Register                  |     |

|      | 4.6.14         | Max Power For Bus-Powered Operation (MAXPB) Register.                  |     |

|      | 4.6.15         | Hub Controller Max Current For Self-Powered Operation (HCMCS) Register |     |

|      | 4.6.16         | Hub Controller Max Current For Bus-Powered Operation (HCMCB) Register  |     |

|      | 4.6.17         | Power-On Time (PWRT) Register                                          |     |

|      | 4.6.18         | Boost Up (BOOSTUP) Register                                            |     |

|      | 4.6.19         | Boost 3:2 (BOOST32) Register                                           |     |

|      | 4.6.20         | Port Swap (PRTSP) Register                                             |     |

|      | 4.6.21         | Port Remap 12 (PRTR12) Register                                        |     |

|      | 4.6.22         | Port Remap 3 (PRTR3) Register                                          |     |

|      | 4.6.23         | Status/Command (STCD) Register                                         |     |

|      |                |                                                                        |     |

| Char | oter 5 (       | Operational Characteristics                                            | 235 |

| 5.1  |                | Maximum Ratings*                                                       |     |

| 5.2  |                | g Conditions**                                                         |     |

| 5.3  | •              | consumption                                                            |     |

| 0.0  | 5.3.1          | SUSPEND0                                                               |     |

|      | 5.3.2          | SUSPEND1                                                               |     |

|      | 5.3.3          | SUSPEND2                                                               |     |

|      |                |                                                                        |     |

|      | 5.3.4    | Operational Current Consumption & Power Dissipation | 237 |

|------|----------|-----------------------------------------------------|-----|

| 5.4  | DC Spec  | sifications                                         | 238 |

| 5.5  | AC Spec  | ifications                                          | 240 |

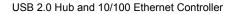

|      | 5.5.1    | Equivalent Test Load.                               | 240 |

|      | 5.5.2    | Reset Timing                                        | 240 |

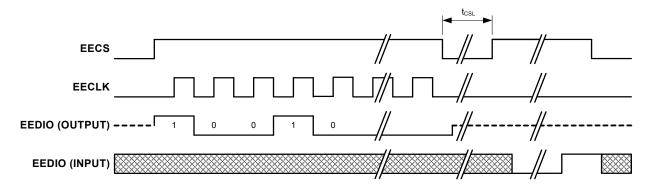

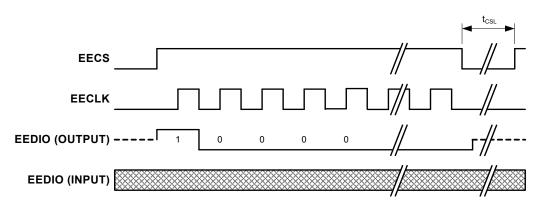

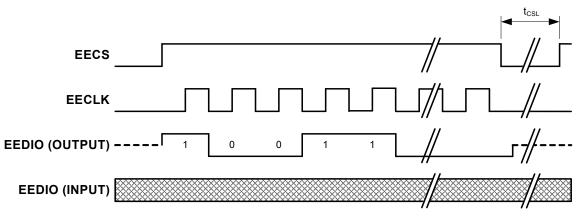

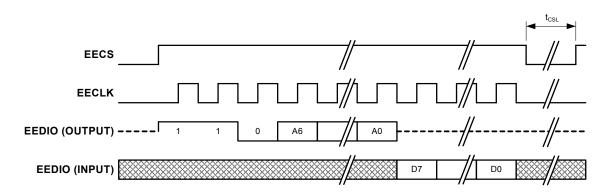

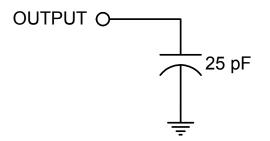

|      | 5.5.3    | EEPROM Timing                                       | 241 |

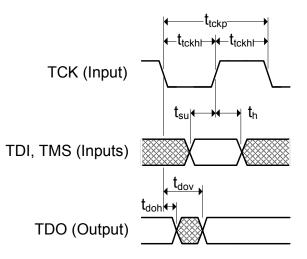

|      | 5.5.4    | JTAG Timing                                         | 242 |

| 5.6  | Clock Ci | rcuit                                               |     |

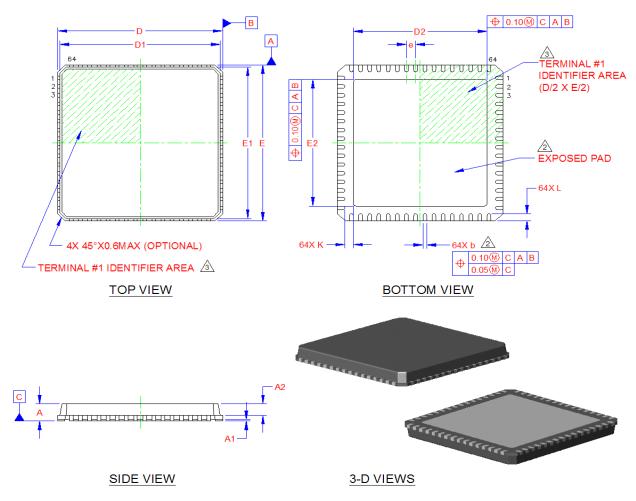

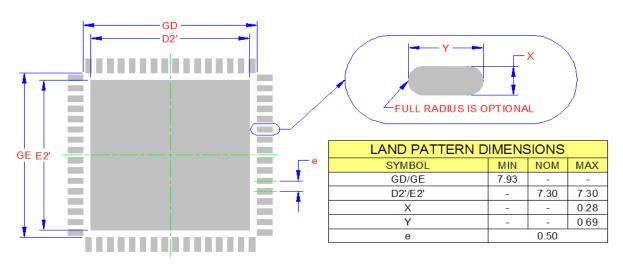

| Chap | oter 6 H | Package Outline                                     | 244 |

| 6.1  | 64-QFN   | Package                                             | 244 |

| Chap | oter 7 I | Databook Revision History                           | 246 |

# List of Figures

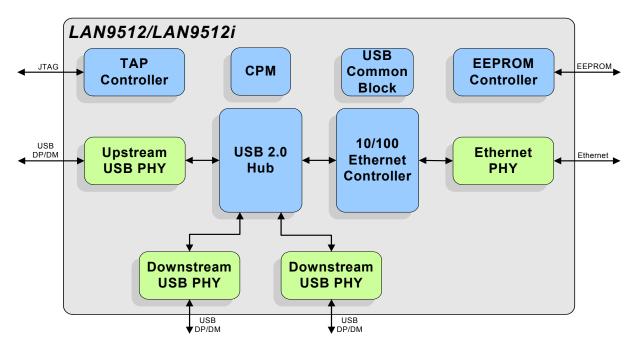

| Figure 1.1 | Internal Block Diagram                                    | 14  |

|------------|-----------------------------------------------------------|-----|

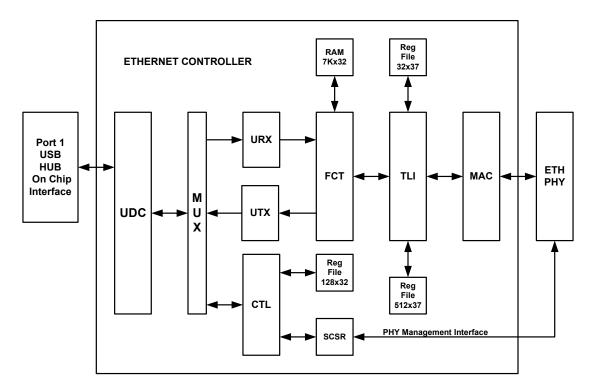

| Figure 1.2 | Ethernet Controller Block Diagram                         |     |

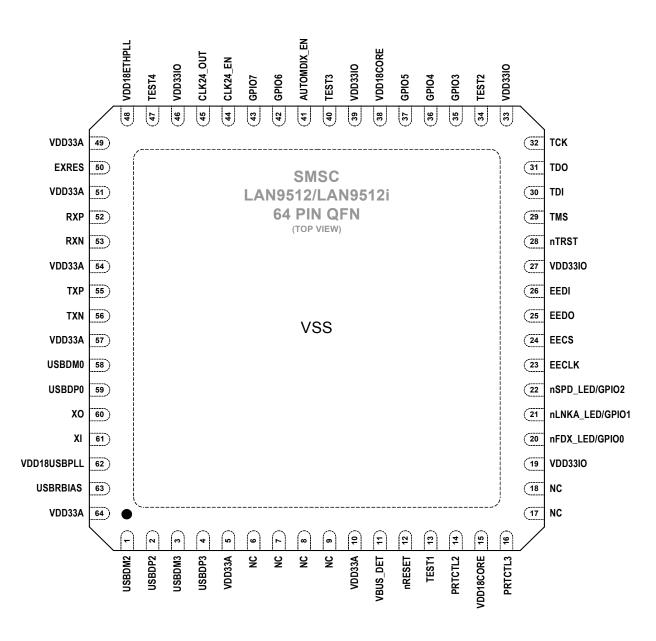

| Figure 2.1 | LAN9512/LAN9512i 64-QFN Pin Assignments (TOP VIEW)        | 20  |

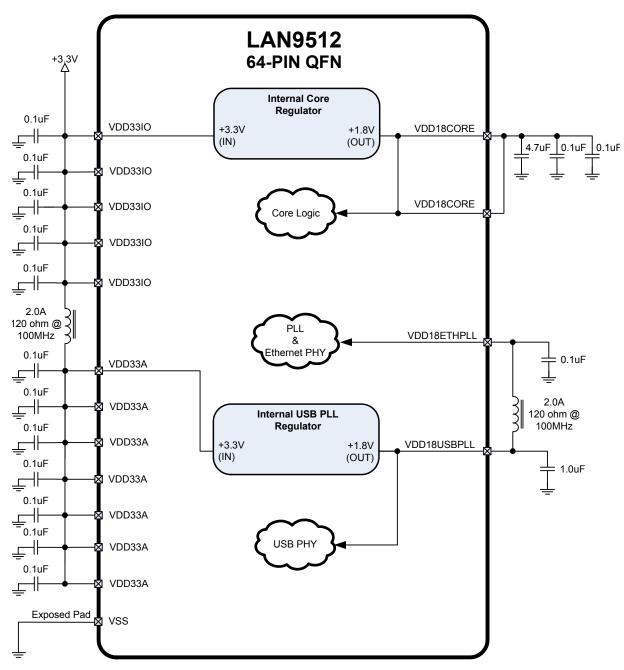

| Figure 2.2 | Power Connections                                         |     |

| Figure 2.3 | Port Power Control with USB Power Switch                  |     |

| Figure 2.4 | Port Power Control with Poly Fuse                         | 29  |

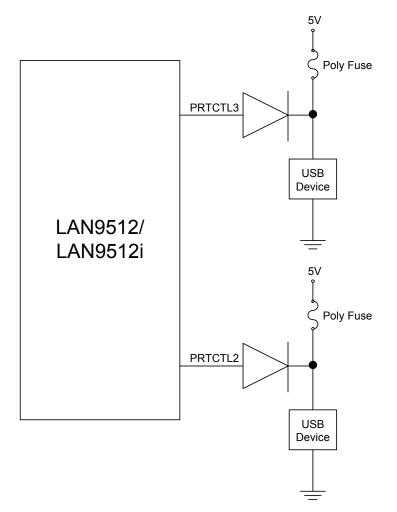

| Figure 2.5 | Port Power with Ganged Control with Poly Fuse             | 30  |

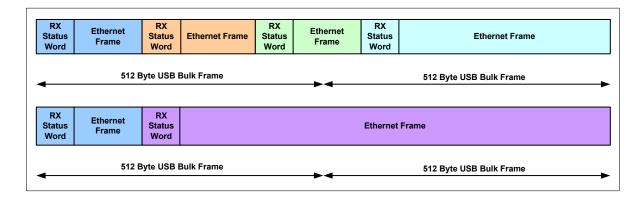

| Figure 3.1 | MEF USB Encapsulation                                     |     |

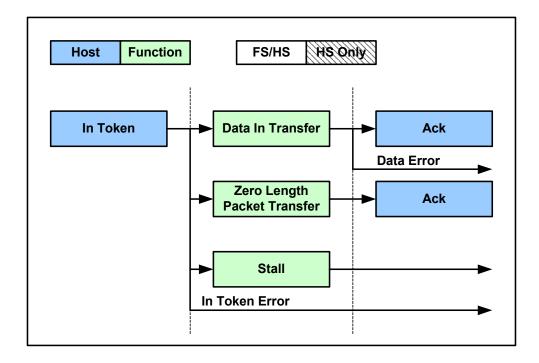

| Figure 3.2 | USB Bulk In Transaction Summary                           |     |

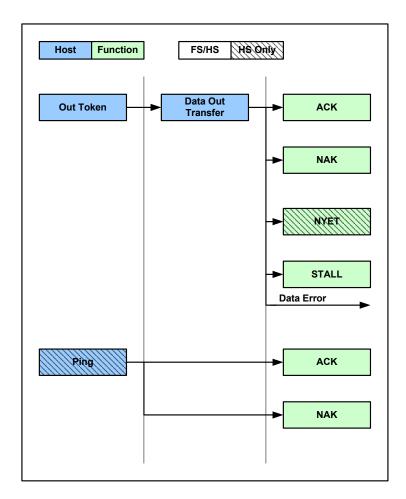

| Figure 3.3 | USB Bulk Out Transaction Summary                          |     |

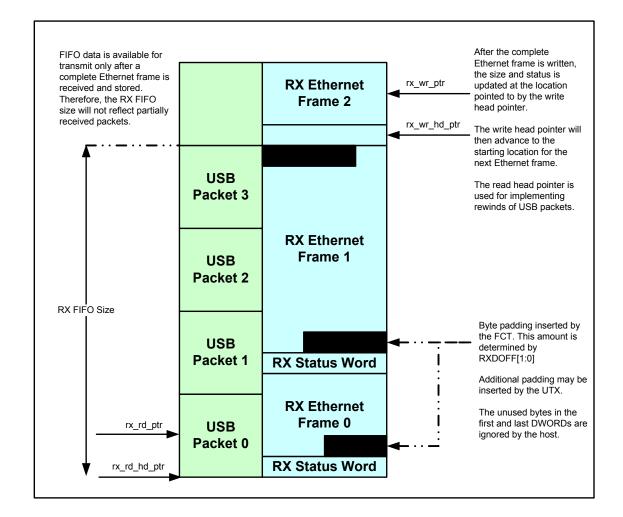

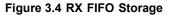

| Figure 3.4 | RX FIFO Storage                                           |     |

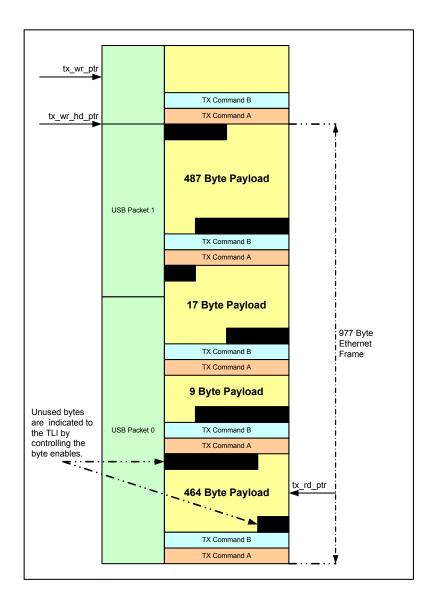

| -          | TX FIFO Storage                                           |     |

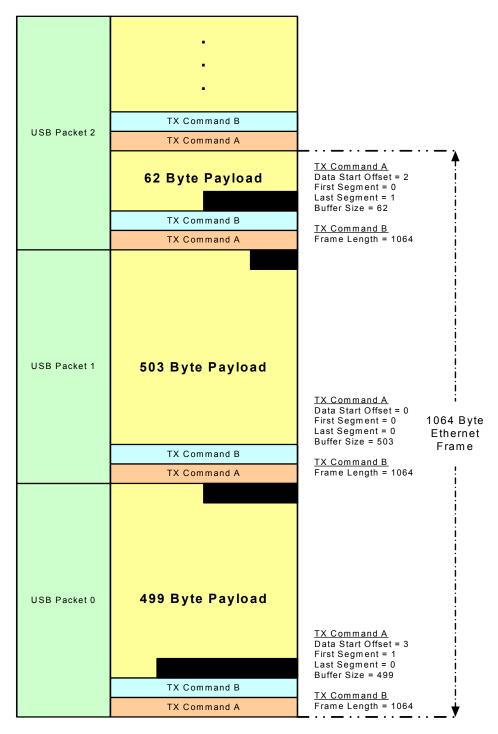

|            | TX Example 1                                              |     |

| -          | TX Example 2                                              |     |

|            | TX Example 3                                              |     |

| •          | VLAN Frame                                                |     |

|            | RXCOE Checksum Calculation                                |     |

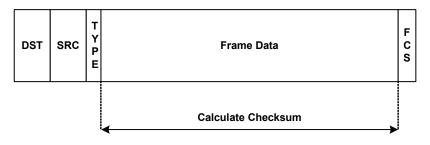

|            | Type II Ethernet Frame                                    |     |

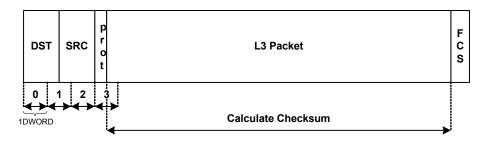

| •          | Ethernet Frame with VLAN Tag                              |     |

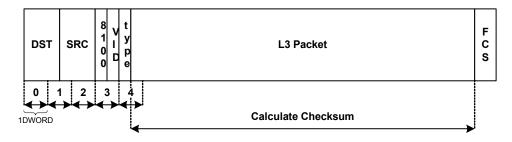

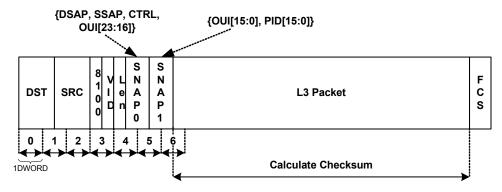

|            | Ethernet Frame with Length Field and SNAP Header          |     |

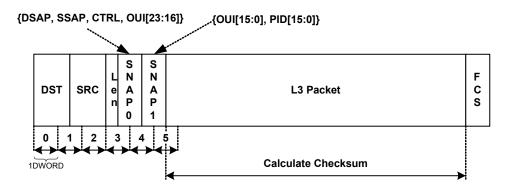

|            | Ethernet Frame with VLAN Tag and SNAP Header.             |     |

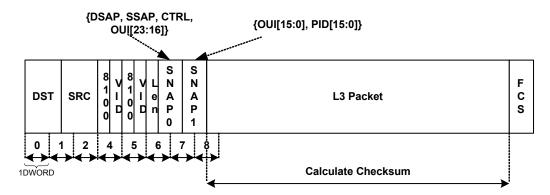

|            | Ethernet Frame with multiple VLAN Tags and SNAP Header    |     |

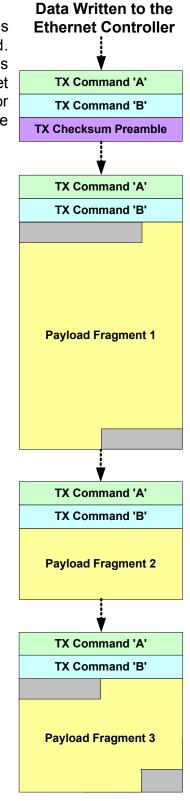

|            | TX Example Illustrating a Pre-pended TX Checksum Preamble |     |

|            | 100Base-TX Data Path                                      |     |