# ATMX150RHA

# PLL400MRHA 40 MHz to 450 MHz Programmable PLL

### Introduction

PLL400MRHA is a core macro-cell designed for synthesizing and synchronizing a chip clock signal from a reference (internal or external) input clock. The main features are:

- Wide output frequency range (40 MHz to 450 MHz)

- Outputs with different phases (0°, 90°, 180°, and 270°)

- Dedicated power supply rails (vccpll and vsspll)

#### Table 1. General Characteristics

| Parameter      | Value      |

|----------------|------------|

| Supply Voltage | 1.8V       |

| Placement      | Core       |

| Height         | 575.1 μm   |

| Width          | 411.5 µm   |

| Area           | 236654 μm² |

# **Table of Contents**

| Introduction1             |                                           |                                 |    |  |  |

|---------------------------|-------------------------------------------|---------------------------------|----|--|--|

| 1.                        | Pin Description                           |                                 |    |  |  |

| 2.                        | Opera                                     | ating Modes Description         | 5  |  |  |

| 3.                        | Speci                                     | fications                       | 6  |  |  |

| 4.                        | Radia                                     | tion Hardness                   | 7  |  |  |

| 5.                        | Funct                                     | ional Description               | 8  |  |  |

|                           | 5.1.                                      | Phase/Frequency Detector        | 8  |  |  |

|                           | 5.2.                                      | Charge Pump                     |    |  |  |

|                           | 5.3.                                      | VCO                             | 9  |  |  |

|                           | 5.4.                                      | Internal Filter                 | 10 |  |  |

|                           | 5.5.                                      | Lock Detector                   | 11 |  |  |

|                           | 5.6.                                      | Typical Application             | 12 |  |  |

| 6.                        | Testal                                    | bility Requirements             | 14 |  |  |

| 7.                        | Integr                                    | ation Guidelines                | 15 |  |  |

|                           | 7.1.                                      | Placement and General Rules     | 15 |  |  |

|                           | 7.2.                                      | Supplies Routing and Decoupling |    |  |  |

|                           | 7.3.                                      | Analog Signals Routing          | 15 |  |  |

|                           | 7.4.                                      | Routing Constraints             | 16 |  |  |

| 8.                        | Revis                                     | ion History                     | 17 |  |  |

| The                       | Micro                                     | chip Website                    | 18 |  |  |

| Pro                       | duct Cl                                   | hange Notification Service      | 18 |  |  |

| Cus                       | tomer                                     | Support                         |    |  |  |

| Mic                       | Microchip Devices Code Protection Feature |                                 |    |  |  |

| Leg                       | Legal Notice                              |                                 |    |  |  |

| Trademarks                |                                           |                                 |    |  |  |

| Quality Management System |                                           |                                 |    |  |  |

|                           |                                           |                                 |    |  |  |

| VVO                       | Worldwide Sales and Service20             |                                 |    |  |  |

### 1. Pin Description

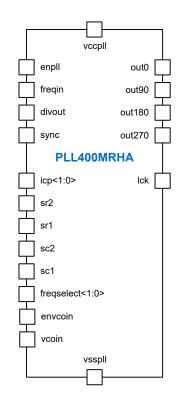

The following figure shows the pinout diagram of PLL400MRHA. Figure 1-1. Pinout Diagram

The following table lists the pins and their functions.

### Table 1-1. Pinout

| Name            | Direction | Related Supply | Description                               |

|-----------------|-----------|----------------|-------------------------------------------|

| vccpll          | power     | NA             | Dedicated power supply                    |

| vsspll          | ground    | NA             | Dedicated ground supply                   |

| enpll           | input     | vccpll         | PLL enable (active-high)                  |

| freqselect<1:0> | input     | vccpll         | VCO frequency range selection bits        |

| icp<1:0>        | input     | vccpll         | Charge Pump current selection bits        |

| sr1             | input     | vccpll         | Internal filter resistance selection bit  |

| sr2             | input     | vccpll         | Internal filter resistance selection bit  |

| sc1             | input     | vccpll         | Internal filter capacitance selection bit |

| sc2             | input     | vccpll         | Internal filter capacitance selection bit |

| freqin          | input     | vccpll         | Phase/Frequency reference input           |

| divout          | input     | vccpll         | Phase/Frequency feedback input            |

| out0            | output    | vccpll         | 0° phase shift VCO output                 |

| out90           | output    | vccpll         | 90° phase shift VCO output                |

# ATMX150RHA

### **Pin Description**

| continued |           |                |                                         |  |  |

|-----------|-----------|----------------|-----------------------------------------|--|--|

| Name      | Direction | Related Supply | Description                             |  |  |

| out180    | output    | vccpll         | 180° phase shift VCO output             |  |  |

| out270    | output    | vccpll         | 270° phase shift VCO output             |  |  |

| lck       | output    | vccpll         | Phase/Frequency lock indicator          |  |  |

| envcoin   | input     | vccpll         | VCO external input enable (active-high) |  |  |

| vcoin     | input     | NA             | VCO external input (analog voltage)     |  |  |

| sync      | input     | vccpll         | out0 phase lock enable (active-high)    |  |  |

**Note:** The pins envcoin and vcoin are used to characterize the PLL. When envcoin = '1', the analog voltage applied on vcoin must not exceed the power supply voltage of the PLL. In normal mode, envcoin = '0', vcoin can be connected to vsspll.

The pin sync enables the out0 Phase Lock mode. The PLL generates the relevant output frequency but locks the phase on out0 instead of that on divout.

# 2. Operating Modes Description

The following table describes the available functional modes. **Table 2-1. Functional Modes**

| enpll | envcoin | sync | Description                                                           |

|-------|---------|------|-----------------------------------------------------------------------|

| 0     | x       | x    | The PLL is disabled.                                                  |

| 1     | 0       | 0    | The PLL is enabled and in Normal mode.                                |

| 1     | 1       | 0    | The PLL is enabled and the pin vcoin is available to control the VCO. |

| 1     | 0       | 1    | The PLL is enabled and locks the phase on out0.                       |

| 1     | 1       | 1    | This is forbidden configuration.                                      |

### 3. Specifications

The following table lists the electrical characteristics of PLL400MRHA. Table 3-1. Electrical Characteristics

| Parameter          |                                                   | Test Conditions                      | Min  | Тур | Max  | Unit |

|--------------------|---------------------------------------------------|--------------------------------------|------|-----|------|------|

| vccpll             | Analog power supply                               |                                      | 1.65 | 1.8 | 1.95 | V    |

| Tj                 | Junction temperature                              |                                      | -55  | 25  | 145  | °C   |

| F <sub>in</sub>    | Reference input frequency                         |                                      | 8    |     | 200  | MHz  |

| Fout               | Output frequency                                  |                                      | 40   |     | 450  | MHz  |

| Nf                 | Frequency ratio F <sub>out</sub> /F <sub>in</sub> |                                      |      |     | 16   |      |

| DC                 | OVCO output duty cycle                            |                                      | 45   |     | 55   | %    |

| P <sub>acc</sub>   | Phase accuracy                                    | out90 vs out0 or out270 vs<br>out180 | -5   |     | 5    | 0    |

| J <sub>per</sub>   | Output period jitter                              |                                      |      |     | 750  | ps   |

| Idd <sub>on</sub>  | ON PLL consumption current                        | enpll = '1' and max F <sub>out</sub> |      |     | 9    | mA   |

| Idd <sub>off</sub> | OFF PLL consumption current                       | Enpll = '0'                          |      |     | 50   | μA   |

**Note:** Suppose  $t_n$  is the sequence of transition times from the output signal and that the nominal period of the reference input signal is T, the output period jitter  $J_{per} = abs ((t_{n+1} - t_n) - T)$ .  $J_{per}$  varies a lot depending on the PLL configuration. Contact Microchip design centers to get the relevant configuration for your application.

### 4. Radiation Hardness

The following table lists the parameters of radiation hardness. **Table 4-1. Radiation Hardness**

| Parameter | Condition                                               |                         |

|-----------|---------------------------------------------------------|-------------------------|

| TID       | ESCC 22900 and Mil-Std 883 TM 1019.5 - 25°C             | 100 kRads (Si) RHA-R    |

|           | Total dose rate of 300 rad/h                            | (tested 150 kRads (Si)) |

| SEL       | ESCC 25100 and JESD57A                                  | > 60 MeV.cm²/mg         |

|           | Input supply voltage vccpll max and Tj = 125°C          |                         |

| SEU       | Input supply voltage vccpll min and Tj = $25^{\circ}$ C | > 30 MeV.cm²/mg         |

### 5. Functional Description

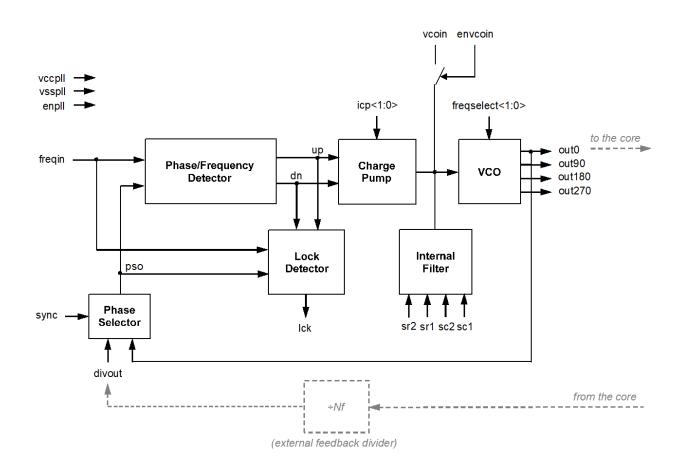

The following sections describe the various components of PLL400MRHA. Figure 5-1. Functional Block Diagram

### 5.1 Phase/Frequency Detector

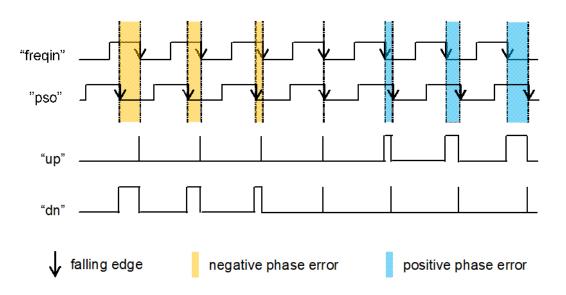

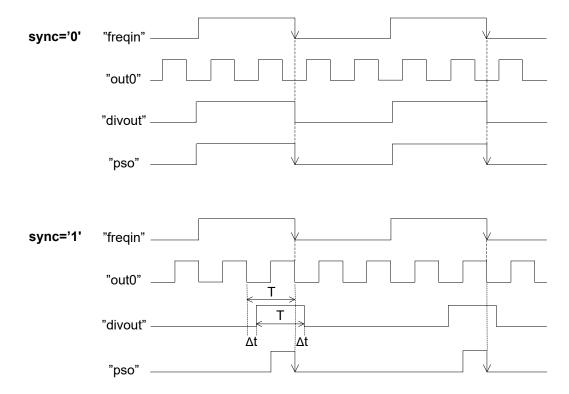

The Phase/Frequency Detector (PFD) is a digital sequential circuit that detects the phase errors between two signals and converts them into two pulse width modulated signals, "up" and "dn". Pulses of "up" indicate that the phase errors are positive while pulses of "dn" are generated for negative phase errors. The PFD compares the falling edge of the reference signal on "freqin" with the falling edge of the Phase Selector output signal "pso".

#### Figure 5-2. Phase Diagram

### 5.2 Charge Pump

The charge pump converts the signals "up" and "dn" into positive and negative currents that charge and discharge the PLL internal filter. The positive current increases the VCO input voltage and the output frequency, while the negative current decreases the VCO input voltage and the output frequency. The charge pump current amplitude lcp can be tuned with the selection pins icp<1:0>.

#### Table 5-1. Charge Pump Truth Table

| icp<1:0> | lcp (μΑ) |     |  |

|----------|----------|-----|--|

|          | Min      | Мах |  |

| 00       | 4.5      | 10  |  |

| 01       | 6.75     | 15  |  |

| 10       | 9        | 20  |  |

| 11       | 11.25    | 25  |  |

### 5.3 VCO

Four VCOs with different frequency ranges and gains are available to generate the output frequencies of the PLL. As per the required output frequencies, a VCO can be selected with appropriate pins freqselect<1:0>.

#### Table 5-2. Frequency Ranges and Gain Variations

| freqselect<1:0> | Frequency Range (MHz) |         | Gain (MHz/V) |         |  |

|-----------------|-----------------------|---------|--------------|---------|--|

|                 | Minimum               | Maximum | Minimum      | Maximum |  |

| 00              | 40                    | 80      | 110          | 160     |  |

| 01              | 70                    | 150     | 180          | 280     |  |

| 10              | 125                   | 275     | 300          | 500     |  |

| 11              | 250                   | 450     | 550          | 1150    |  |

### 5.4 Internal Filter

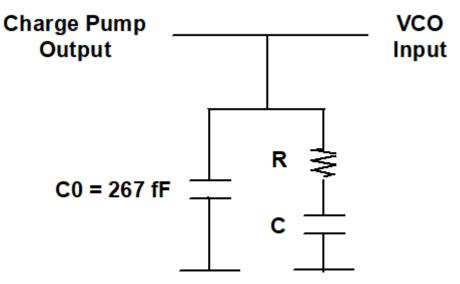

The internal filter is made up of a built-in capacitor C0 in parallel with a resistor R and a capacitor C in series. **Figure 5-3. Internal Filter**

The resistance of R and the capacitance of C depend on the pins sr2, sr1, sc2, and sc1 setting. **Table 5-3. Resistence Options**

| sr2 sr1 | Resistance (kΩ) |

|---------|-----------------|

| 00      | 24              |

| 01      | 6               |

| 10      | 3               |

| 11      | 12              |

#### Table 5-4. Capacitance Options

| sc2 sc1 | Capacitance (pF) |

|---------|------------------|

| 00      | 20               |

| 01      | 40               |

| 10      | 30               |

| 11      | 60               |

#### Notes:

- 1. Microchip design center determines the relevant PLL configuration, freqselect<1:0>, icp<1:0>, sr2, sr1, sc2, and sc1 setting, according to your application needs. However, several configuration pins like icp<1:0> must be primary inputs of the design in order to better control the performance of the PLL.

- 2. It is recommended to allow reprogramming the configuration pins to better adjust the PLL stability and reduce its output jitter. For example, the pins icp<1:0> can be primary inputs used to find the best setting and then hard biased on the PCB. If the configuration pins setting is stored in a register, then the latter has to be radiation hardened.

#### 5.4.1 Phase Selector

The phase selector generates the signal "pso", which is compared with the reference signal "freqin".

- If sync = '0' then "pso" = "divout" → signal phase lock on divout (clock deskewing)

- If sync = '1' then "pso" = "out0" and "divout" → signal phase lock on out0 (output phase control)

#### Figure 5-4. Phase Selector Characteristics

If sync = '1', then the external feedback divider is a counter that generates a pulse = '1' every Nf periods of "out0".

It has to be designed according to the following rules:

- The pulse rising and falling edges must be triggered by the falling edges of "out0".

- The pulse width must be equal to T, the period of "out0", so,  $Nf \ge 2$ .

- "out0" is not used directly but its buffered one, which is "1 gate delay" late. Let Δt be the feedback divider propagation delay, "1gate delay" ≤ Δt ≤ "1 gate delay" + (T/2).

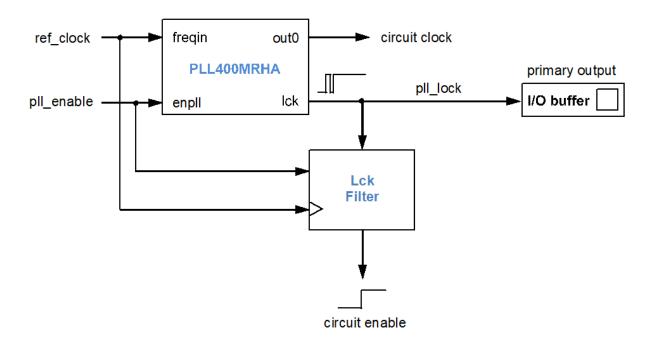

### 5.5 Lock Detector

The lock detector indicates if the PLL is Phase/Frequency locked.

- Phase/Frequency locked → lck = '1' When the phase difference between the falling edges of the signals "pso" and "freqin" is lower than half the period of "freqin", for 12 consecutive periods of "freqin".

- Phase/Frequency unlocked → lck = '0' As soon as the phase difference between the falling edges of the signals "pso" and "freqin" exceeds half the period of "freqin".

Note: Ick = '0' or Ick = '1' when the PLL is disabled. Ick is only reset (Ick = '0') at PLL startup.

The signal "lck" must not be used directly to enable/disable a circuit. It has to be "filtered".

Figure 5-5. Lock Detector Circuit

In the above circuit, the PLL lock signal "pll\_lock" is propagated to a primary output I/O buffer and is used by the Lck filter to generate a delayed and stable circuit enable signal. The circuit enable signal is reset as soon as pll\_enable = '0' or pll\_lock = '0'.

**Note:** Radiation particles or a phase/frequency disruption of the reference signal "freqin" can reset the lock signal (lck = '0') while the PLL is still phase/frequency locked. In this case, the PLL has to be restarted to get a correct PLL lock signal again. Once the PLL is Phase/Frequency locked, a disruption of the reference signal "freqin" can reset the PLL lock signal, lck = '0' while the PLL is still Phase/Frequency locked. In this case, the PLL has to be restarted to get a correct PLL lock signal again.

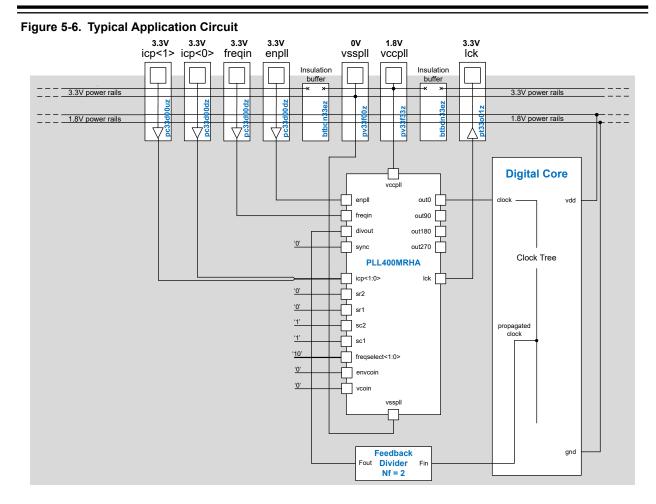

### 5.6 Typical Application

In this typical application, PLL400MRHA generates a clock signal for the digital core. The clock signal on out0 is propagated in the clock tree of the digital core, then its frequency is divided by Nf = 2 and the resulting signal on divout is compared with the reference signal on freqin. When the PLL is Phase/Frequency locked, the frequency of the propagated clock signal, in the digital core, is twice higher than that of the reference one and its falling edges are in phase with those of the reference one. The lock signal of the PLL on lck is propagated to a primary output. The behavior of the PLL can slightly change in setting the input pins icp<0> and icp<1>. Thus, the phase/frequency lock time and the output signal jitter can be reduced.

### 6. Testability Requirements

Unless otherwise specified at the DSR, the lock is to be checked and Fout, the output frequency parameters, is to be measured.

For these tests:

- The external feedback divider must be connected to the PLL and should be enabled before the PLL startup.

- The reference signal on freqin must be compliant with the PLL specifications.

- The relevant PLL configuration must be given by a Microchip design center.

- The lock signal on lck must be propagated to a primary output to assess the PLL lock.

The PLL must be Phase/Frequency locked in less than 100 µs.

It is recommended to measure the PLL output frequency to confirm that the PLL is Phase/Frequency locked. So, the PLL output signal on out0 can also be propagated to a primary output in order to extract the PLL output frequency, the duty cycle, and the jitter. If the signal frequency is too high (>100 MHz) for a digital output buffer or too high (>320 MHz) for a LVDS buffer then its frequency has to be divided before being propagated.

### 7. Integration Guidelines

The following sections provide guidelines for efficient sytem integration.

### 7.1 Placement and General Rules

The PLL is a noisy and sensitive circuit that has to be placed far from the digital core and other analog blocks. It has to be close to the I/O buffers it is connected to and the wires used to connect the PLL must be as wide as its corresponding pins.

The PLL does not include the feedback divider. It must be placed near the PLL but without disturbing each other.

Configuration pins should be primary inputs of the design to better control the stability and the performance of the PLL. At least, icp<1:0> should be reprogrammable. If the configuration pins setting is stored in a register then the latter has to be radiation hardened.

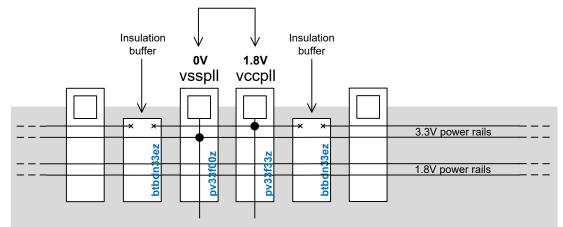

### 7.2 Supplies Routing and Decoupling

The PLL has its own power supply pins, vccpll, and vsspll. They are connected to specific power supply buffers which are separated from the others by insulation buffers. The routing resistances between the pins of the power supply/ ground buffers and the power supply/ground pins of the PLL must not be higher than 5  $\Omega$ . To reduce the noise coupling, vccpll should be connected to a dedicated package cavity\_pad/lead.

- Ground buffer for vsspll pv33f00z

- Power supply buffer for vccpll pv33f33z

- Insulation buffer btbdn33ez

#### Figure 7-1. Ground and Power Supply Buffers

**Note:** Unless otherwise noted, all the power supplies must be decoupled externally with large capacitors, 1 uF//10 nF.

### 7.3 Analog Signals Routing

The analog signal vcoins must be routed to have less than 51  $\Omega$  resistance, from the source to the sink.

The signal routed to the pin vcoin is an analog voltage and all digital or clock signals must be routed with 1  $\mu$ m spacing away from this signal. In case of crossing digital or clock signals, a shield connected to the analog ground is required between the noisy net and the analog signal.

If these conditions are not met, contact the design group Microchip design centers to investigate potential performance impact.

### 7.4 Routing Constraints

The following table lists the routing constraints for PLL400MRHA.

#### Table 7-1. Routing Constraints

| Pin Name            | Signal<br>Type | Related<br>Power<br>Supply | Max DC<br>Current<br>Flowing<br>(mA) | Max allowed<br>Routing<br>Resistance<br>(Ω) | Max Allowed<br>Capacitance<br>to Ground<br>(pF) | Other Constraints                                                                                                          |

|---------------------|----------------|----------------------------|--------------------------------------|---------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| vccpll              | Supply         | -                          | 9                                    | 5                                           | -                                               | Star routing to power supply.                                                                                              |

| vsspll              | Ground         | -                          | -                                    | 5                                           | -                                               | Star routing to ground.                                                                                                    |

| enpll               | Digital        | vccpll                     | -                                    | -                                           | -                                               |                                                                                                                            |

| freqselect<1:0<br>> | Digital        | vccpll                     | -                                    | -                                           | -                                               |                                                                                                                            |

| icp<1:0>            | Digital        | vccpll                     | -                                    | -                                           | -                                               |                                                                                                                            |

| sr1                 | Digital        | vccpll                     | -                                    | -                                           | -                                               |                                                                                                                            |

| sr2                 | Digital        | vccpll                     | -                                    | -                                           | -                                               |                                                                                                                            |

| sc1                 | Digital        | vccpll                     | -                                    | -                                           | -                                               |                                                                                                                            |

| sc2                 | Digital        | vccpll                     | -                                    | -                                           | -                                               |                                                                                                                            |

| freqin              | Digital        | vccpll                     | -                                    | -                                           | -                                               |                                                                                                                            |

| divout              | Digital        | vccpll                     | -                                    | -                                           | -                                               |                                                                                                                            |

| out0                | Digital        | vccpll                     | -                                    | -                                           | -                                               |                                                                                                                            |

| out90               | Digital        | vccpll                     | -                                    | -                                           | -                                               |                                                                                                                            |

| out180              | Digital        | vccpll                     | -                                    | -                                           | -                                               |                                                                                                                            |

| out270              | Digital        | vccpll                     | -                                    | -                                           | -                                               |                                                                                                                            |

| lck                 | Digital        | vccpll                     | -                                    | -                                           | -                                               |                                                                                                                            |

| envcoin             | Digital        | vccpll                     | -                                    | -                                           | -                                               |                                                                                                                            |

| vcoin               | Analog         | -                          | -                                    | 5                                           | -                                               | No crossing with<br>other signals,<br>otherwise, shielding<br>to vsspll.<br>1 µm minimum<br>spacing from other<br>signals. |

| sync                | Digital        | vccpll                     | -                                    | -                                           | -                                               |                                                                                                                            |

# 8. Revision History

| Revision | Date           | Description                                                                                                                 |

|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------|

| A        | September 2020 | The following is a summary of changes in revision A of this document.                                                       |

|          |                | <ul><li>Updated the document as per Microchip standards.</li><li>Modified the radiation tolerance specifications.</li></ul> |

## The Microchip Website

Microchip provides online support via our website at www.microchip.com/. This website is used to make files and information easily available to customers. Some of the content available includes:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's

guides and hardware support documents, latest software releases and archived software

- **General Technical Support** Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- **Business of Microchip** Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to www.microchip.com/pcn and follow the registration instructions.

# **Customer Support**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Embedded Solutions Engineer (ESE)

- Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: www.microchip.com/support

# Microchip Devices Code Protection Feature

Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

# Legal Notice

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with

your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

### Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TempTrackr, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, Vite, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2020, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-6721-2

## **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# **Worldwide Sales and Service**

| AMERICAS                                  | ASIA/PACIFIC                              | ASIA/PACIFIC                         | EUROPE                                 |

|-------------------------------------------|-------------------------------------------|--------------------------------------|----------------------------------------|

| Corporate Office                          | Australia - Sydney                        | India - Bangalore                    | Austria - Wels                         |

| 2355 West Chandler Blvd.                  | Tel: 61-2-9868-6733                       | Tel: 91-80-3090-4444                 | Tel: 43-7242-2244-39                   |

| Chandler, AZ 85224-6199                   | China - Beijing                           | India - New Delhi                    | Fax: 43-7242-2244-39                   |

| el: 480-792-7200                          | Tel: 86-10-8569-7000                      | Tel: 91-11-4160-8631                 | Denmark - Copenhagen                   |

| ax: 480-792-7277                          | China - Chengdu                           | India - Pune                         | Tel: 45-4485-5910                      |

|                                           | -                                         | Tel: 91-20-4121-0141                 | Fax: 45-4485-2829                      |

| echnical Support:                         | Tel: 86-28-8665-5511                      | Japan - Osaka                        |                                        |

| /ww.microchip.com/support<br>/eb Address: | China - Chongqing<br>Tel: 86-23-8980-9588 | Tel: 81-6-6152-7160                  | Finland - Espoo<br>Tel: 358-9-4520-820 |

| veb Address.<br>/ww.microchip.com         |                                           | Japan - Tokyo                        | France - Paris                         |

| Atlanta                                   | China - Dongguan                          | Tel: 81-3-6880- 3770                 | Tel: 33-1-69-53-63-20                  |

|                                           | Tel: 86-769-8702-9880                     | Korea - Daegu                        |                                        |

| uluth, GA                                 | China - Guangzhou                         |                                      | Fax: 33-1-69-30-90-79                  |

| el: 678-957-9614                          | Tel: 86-20-8755-8029                      | Tel: 82-53-744-4301<br>Korea - Seoul | Germany - Garching                     |

| ax: 678-957-1455                          | China - Hangzhou                          |                                      | Tel: 49-8931-9700                      |

| ustin, TX                                 | Tel: 86-571-8792-8115                     | Tel: 82-2-554-7200                   | Germany - Haan                         |

| el: 512-257-3370                          | China - Hong Kong SAR                     | Malaysia - Kuala Lumpur              | Tel: 49-2129-3766400                   |

| loston                                    | Tel: 852-2943-5100                        | Tel: 60-3-7651-7906                  | Germany - Heilbronn                    |

| Vestborough, MA                           | China - Nanjing                           | Malaysia - Penang                    | Tel: 49-7131-72400                     |

| el: 774-760-0087                          | Tel: 86-25-8473-2460                      | Tel: 60-4-227-8870                   | Germany - Karlsruhe                    |

| ax: 774-760-0088                          | China - Qingdao                           | Philippines - Manila                 | Tel: 49-721-625370                     |

| hicago                                    | Tel: 86-532-8502-7355                     | Tel: 63-2-634-9065                   | Germany - Munich                       |

| asca, IL                                  | China - Shanghai                          | Singapore                            | Tel: 49-89-627-144-0                   |

| el: 630-285-0071                          | Tel: 86-21-3326-8000                      | Tel: 65-6334-8870                    | Fax: 49-89-627-144-44                  |

| ax: 630-285-0075                          | China - Shenyang                          | Taiwan - Hsin Chu                    | Germany - Rosenheim                    |

| allas                                     | Tel: 86-24-2334-2829                      | Tel: 886-3-577-8366                  | Tel: 49-8031-354-560                   |

| ddison, TX                                | China - Shenzhen                          | Taiwan - Kaohsiung                   | Israel - Ra'anana                      |

| el: 972-818-7423                          | Tel: 86-755-8864-2200                     | Tel: 886-7-213-7830                  | Tel: 972-9-744-7705                    |

| ax: 972-818-2924                          | China - Suzhou                            | Taiwan - Taipei                      | Italy - Milan                          |

| etroit                                    | Tel: 86-186-6233-1526                     | Tel: 886-2-2508-8600                 | Tel: 39-0331-742611                    |

| ovi, MI                                   | China - Wuhan                             | Thailand - Bangkok                   | Fax: 39-0331-466781                    |

| el: 248-848-4000                          | Tel: 86-27-5980-5300                      | Tel: 66-2-694-1351                   | Italy - Padova                         |

| ouston, TX                                | China - Xian                              | Vietnam - Ho Chi Minh                | Tel: 39-049-7625286                    |

| el: 281-894-5983                          | Tel: 86-29-8833-7252                      | Tel: 84-28-5448-2100                 | Netherlands - Drunen                   |

| ndianapolis                               | China - Xiamen                            |                                      | Tel: 31-416-690399                     |

| oblesville, IN                            | Tel: 86-592-2388138                       |                                      | Fax: 31-416-690340                     |

| el: 317-773-8323                          | China - Zhuhai                            |                                      | Norway - Trondheim                     |

| ax: 317-773-5453                          | Tel: 86-756-3210040                       |                                      | Tel: 47-72884388                       |

| el: 317-536-2380                          |                                           |                                      | Poland - Warsaw                        |

| os Angeles                                |                                           |                                      | Tel: 48-22-3325737                     |

| lission Viejo, CA                         |                                           |                                      | Romania - Bucharest                    |

| el: 949-462-9523                          |                                           |                                      | Tel: 40-21-407-87-50                   |

| ax: 949-462-9608                          |                                           |                                      | Spain - Madrid                         |

| el: 951-273-7800                          |                                           |                                      | Tel: 34-91-708-08-90                   |

| aleigh, NC                                |                                           |                                      | Fax: 34-91-708-08-91                   |

| el: 919-844-7510                          |                                           |                                      | Sweden - Gothenberg                    |

| ew York, NY                               |                                           |                                      | Tel: 46-31-704-60-40                   |

| el: 631-435-6000                          |                                           |                                      | Sweden - Stockholm                     |

| an Jose, CA                               |                                           |                                      | Tel: 46-8-5090-4654                    |

| el: 408-735-9110                          |                                           |                                      | UK - Wokingham                         |

| el: 408-436-4270                          |                                           |                                      | Tel: 44-118-921-5800                   |

| Canada - Toronto                          |                                           |                                      | Fax: 44-118-921-5820                   |

|                                           |                                           |                                      | Fax. 44-110-921-3020                   |

| el: 905-695-1980                          |                                           |                                      |                                        |

| ax: 905-695-2078                          |                                           |                                      |                                        |